Hi,

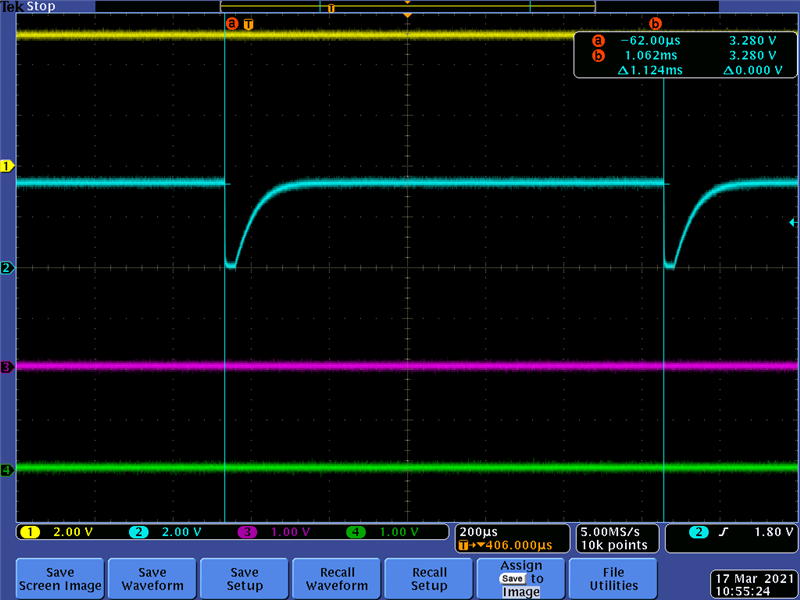

I'm working with F28M35H52C Concerto device installed on our custom-designed application hardware. This is a new design and we performed the first power-up test with no any code loaded to the device so the Concerto device is in its initial off-the-shelf condition. With all the power voltages applied and no signs of overload I started checking the reset signals on the XRS/ARS reset pins. These pins are connected together as recommended by the device documentation. I've found the unexpected pulses on these pins that are only present if device attempts to boot into flash memory. If boot mode is changed to serial interface, these pulses disappear and nXRS = 1 as expected.

My thought is that these reset pulses are triggered by one of the watchdog timers. Upon checking the TRM I've found that WDT1 and WDT0 timers are disabled by default and therefore it's my take that resets are triggered by NMI WDT. But here is where my confusion comes.

The X1 clock in our application is 20 MHz so the clock period is 50 ns. Based on the nXRS waveform provided above, the reset pulse period is 1.124 ms. But, given that NMI WDT is 16-bit counter, I would anticipate that period to be 50ns * 2^16 = 3.2768 ms, which is about 3X the observed period. I'm not sure if it takes 1 or 2 NMI WDT cycles to trigger system reset but the observed period is just the fraction of even a single cycle.

So my questions are as follows below.

Q1: Is it correct that the observed nXRS pulses are caused by the NMI WDT timer? If not, what's the possible source?

Q2: If these pulses are indeed caused by the NMI watchdog, then why is there a discrepancy between the anticipated and observed period values?

Thank you,

Michael