Other Parts Discussed in Thread: LAUNCHXL-F280025C, , TIDM-DC-DC-BUCK, POWERSUITE, C2000WARE, SYSBIOS, SFRA, LAUNCHXL-F280049C

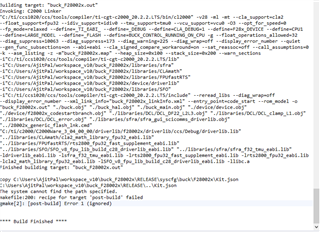

I modified the example code based on F28004x for BOOSTXL-BUCKCONV (in the TIDM-DC-DC-BUCK CONVERTER) to make it run on LAUNCHXL-F280025C.

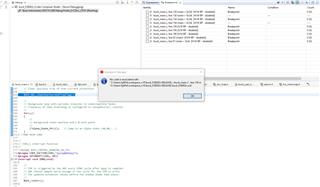

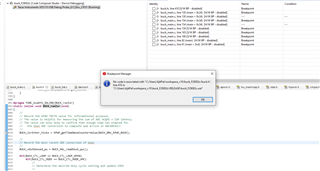

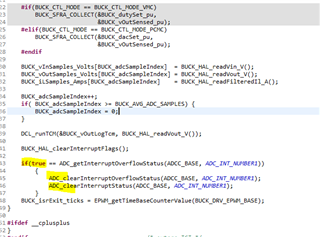

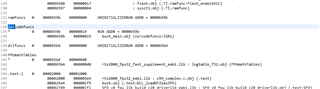

My problem is that the code is not running the ISR is the buck_main.c . As you can see in the image below, the breakpoint in line 159 shows the function there is not a part of the code compiled.

The ISR is below the line 159 and that also is not compiled.

Please help solve this issue asap.