Other Parts Discussed in Thread: C2000WARE

Hi,

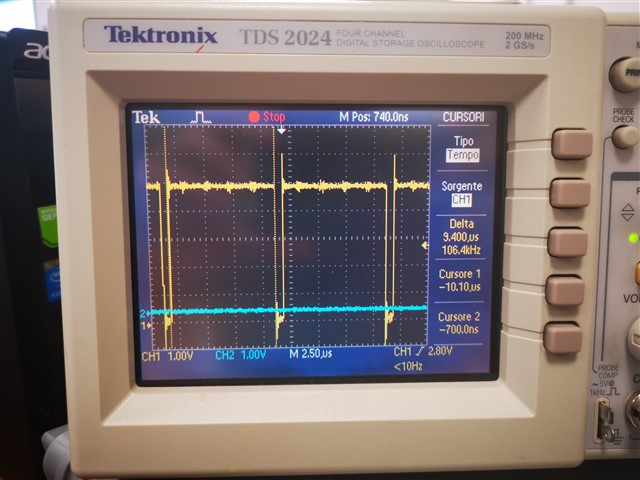

I'm facing a really strange problem on my application. Basically in my app there are 4 EPWM where the pwm#3 triggers ADCs. I decided to measure the occupation time for every single ADC by strobing a GPIO but the stuff I was seeing in oscilloscope was totally different from my expectations.

So I decided to drive the same strobe on main.c (basically an empty main) to check the timing and now the trouble begin.

On this main.c the frequency measured with o-scope is 1.64MHz (but my clock is 100Mhz and I'm only doing 200 sums)

/* Check RAM */

ramCheck(); /* does nothing */

/* Init variables (must be at the code beginning) */

CSU_initVariables();

/* Low level inits */

CSU_InitBoot();

GPIO_InitSafe(); /* does nothing */

duty = 0.5F;

flagConvertTemp = 0;

debugLength = 0;

startMagazzino = 1;

int i = 0;

marco1 = 0;

while (1)

{

GpioDataRegs.GPATOGGLE.bit.GPIO25 = 1;

for (i = 0; i < 200; i++)

{

marcoDebug += 10;

}

marco1 = 0;

switch (marco1)

{

case 1:

marco1 = 0;

CSU_SetPWMDuty(1, duty);

CSU_SetPWMDuty(2, duty);

CSU_SetPWMDuty(3, duty);

CSU_SetPWMDuty(4, duty);

break;

default:

break;

}

}

}

But on this main.c the frequecy is only 7.8KHz (but all the settings are the same)

int32_t main(void)

{

GPIOSTATUS prova;

/* Check RAM */

ramCheck(); /* does nothing */

/* Init variables (must be at the code beginning) */

CSU_initVariables();

/* Low level inits */

CSU_InitBoot();

GPIO_InitSafe(); /* does nothing */

duty = 0.5F;

flagConvertTemp = 0;

debugLength = 0;

startMagazzino = 1;

int i = 0;

marco1 = 0;

while (1)

{

GpioDataRegs.GPATOGGLE.bit.GPIO25 = 1;

for (i = 0; i < 200; i++)

{

marcoDebug += 10;

}

//marco1 = 0;

switch (marco1)

{

case 1:

marco1 = 0;

CSU_SetPWMDuty(1, duty);

CSU_SetPWMDuty(2, duty);

CSU_SetPWMDuty(3, duty);

CSU_SetPWMDuty(4, duty);

break;

default:

break;

}

}

}

I only commented out the line 32, but the code never reaches the "case 1" of the switch becouse the variable is set to 0 on top and no-one changes it so I was expecting no difference at all instead of having a frequency drammatically lowered.

I don't know what could be the problem and I also tried to optimize from the Project --> Properties-->Optimization but nothing.

Seems some kind of memory issue or linker issue or project properties issue and I'm available to share the entire project in PM for further analysis.

P.s. I'm pretty sure the cpu clock from pll is 100MHz because I measured the PWM frequency and it is as expected

Thanks,

M.