Dear Sir,

I am irfan. I have TMS320F28335 DSP starter kit using which I am working our my projects to communicate with my sensors but the problem is the CodeStartBranch.asm file is continuously showing up an error called as " invalid Instruction". I have checked with the problem a lot but still this error is not moving out.

Can anyone suggest me what can I do to remove this? When I am removing the instruction itself, it is showing a lot more errors. I am struck here. Please help.

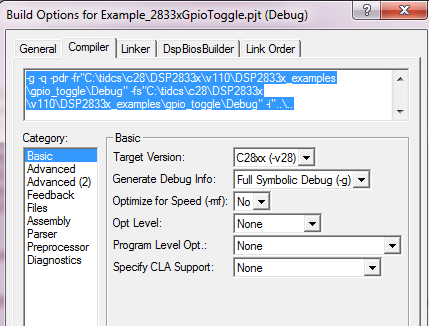

Here I attach the picture of the error Please help me in this regard.

Thanks a lot!

Regards,

Irfan.