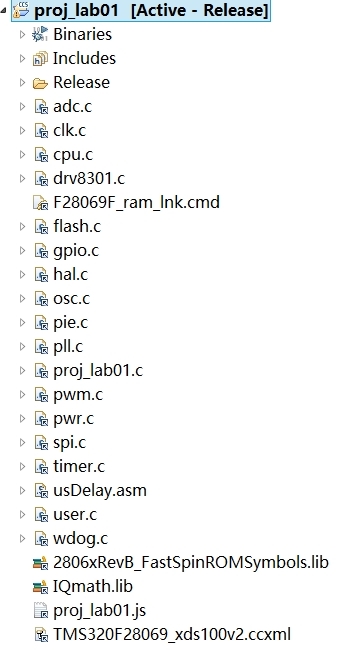

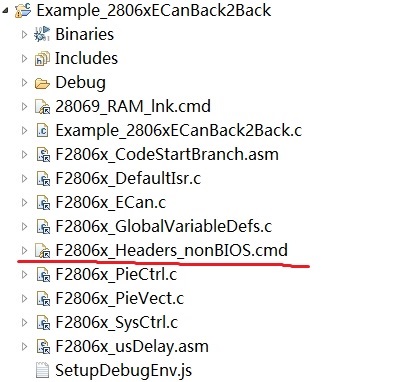

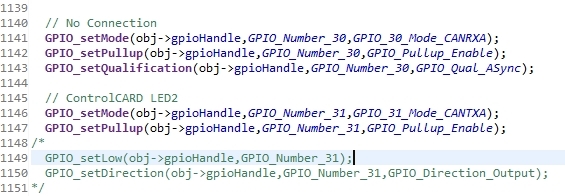

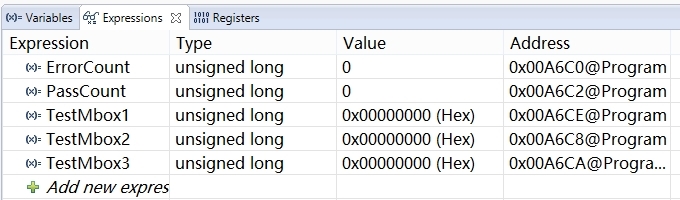

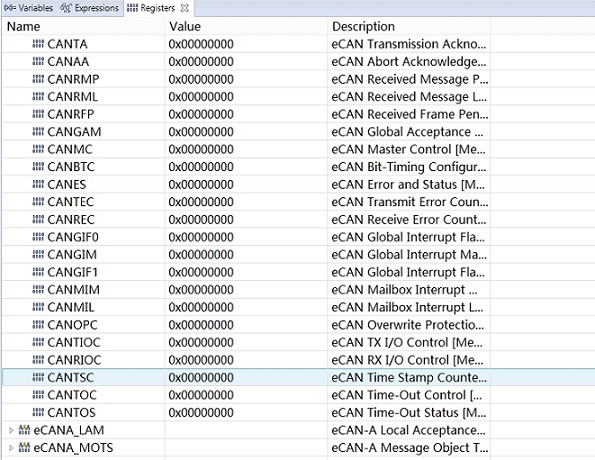

I have achieved CAN communication successfully on TMS320F28069.

But I need to migrate my code in TMS320F28069 to TMS320F28069M.

Does anyone migrate the code to TMS320F28069M successfully? Can you give me this guidance?Or there are some posts or handbooks as a reference?