hi

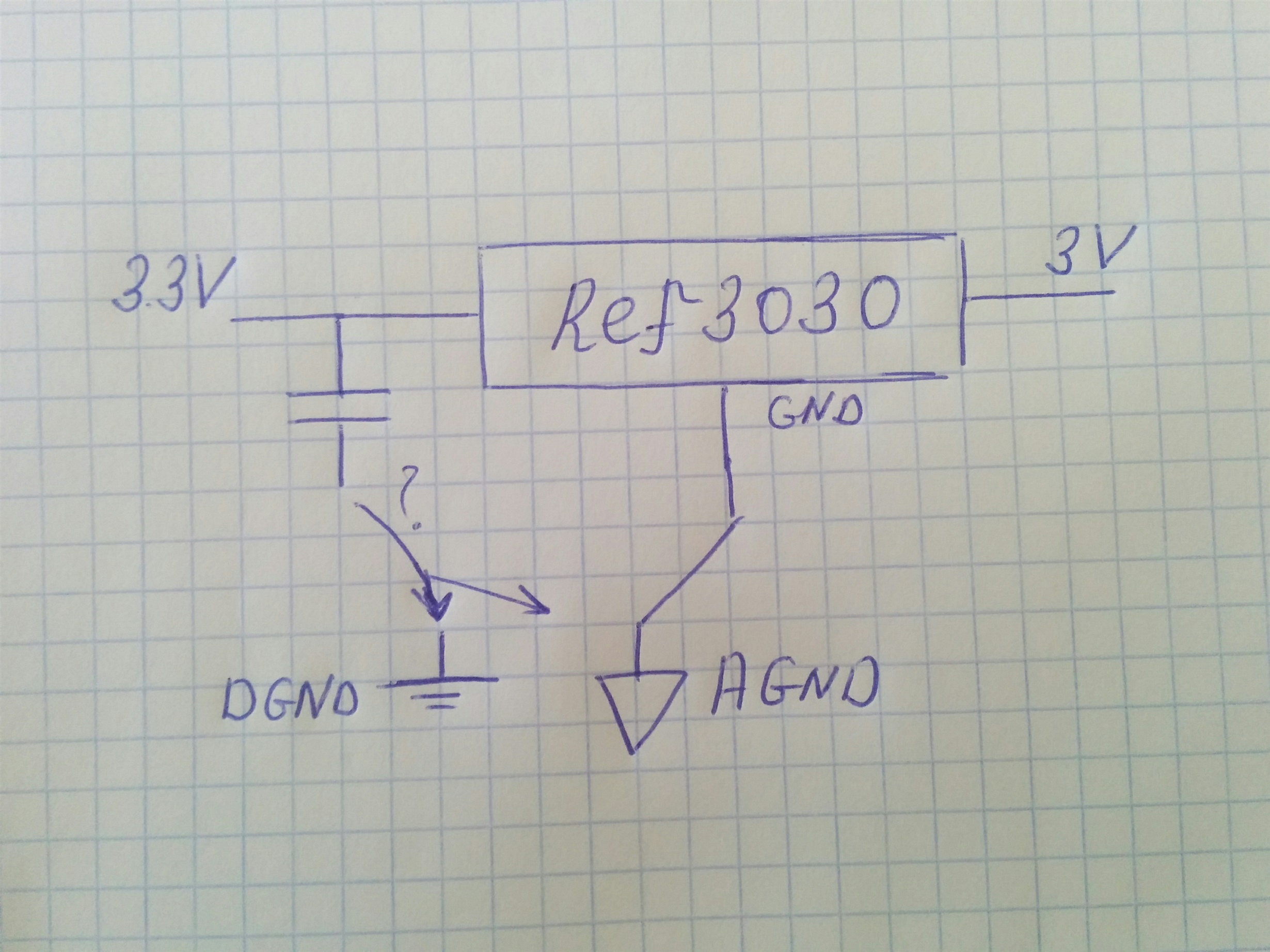

I am designing layout for delfino TMS320F2837xS ,and i am using the REF3030 LDO for ADC VREF,

i have both DGND and AGND, my question is about the REF3030 GND connections :

- should i connect ref3030 ground to the AGND ?

- which ground should i connect to the ref3030 input capacitor?

thank you very much for your help

best regards

Mark