Part Number: TMS320F28379D

Other Parts Discussed in Thread: OPA4350, OPA350, REF2030

Hi,

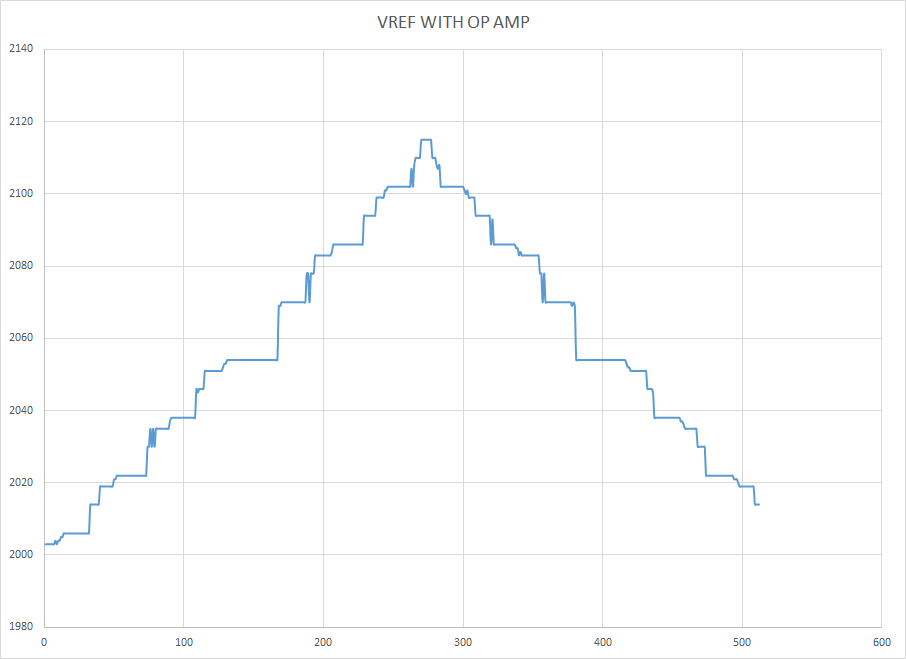

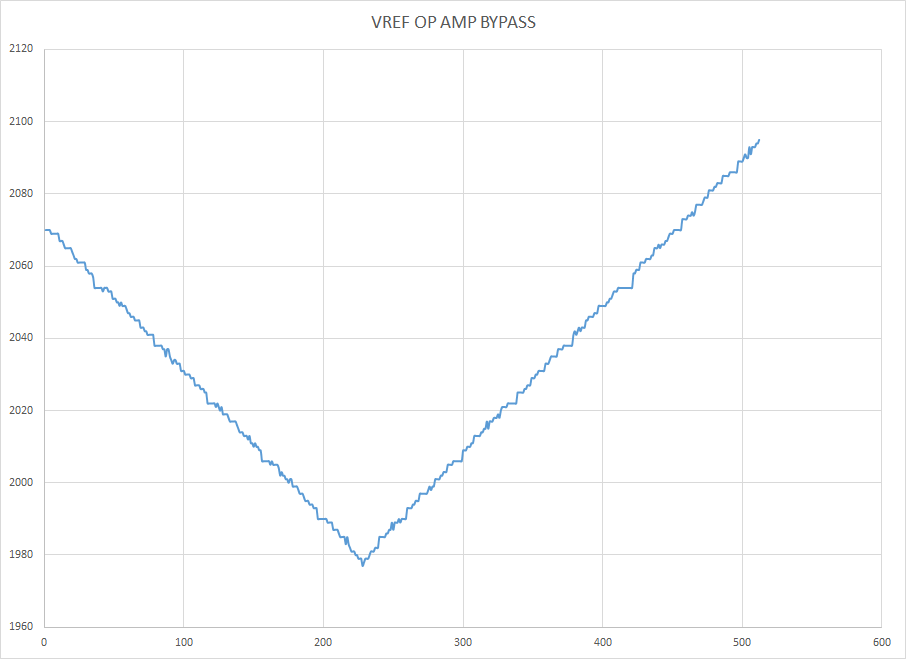

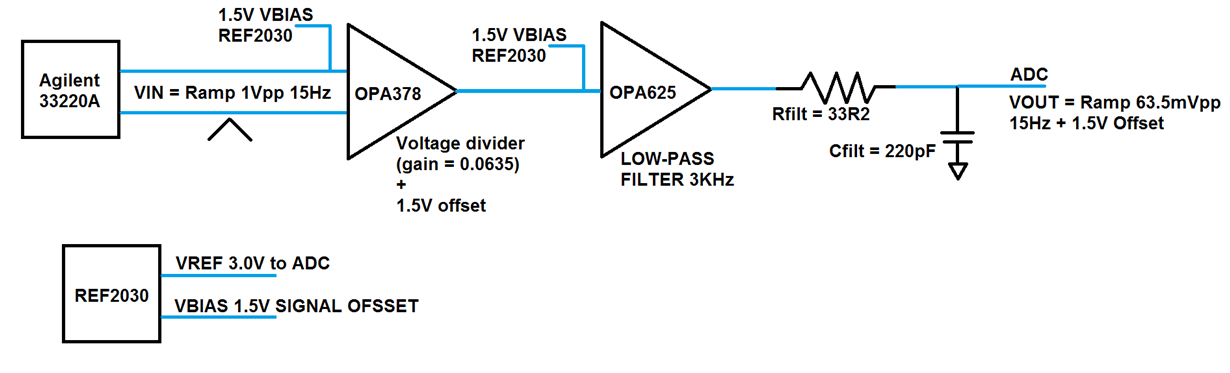

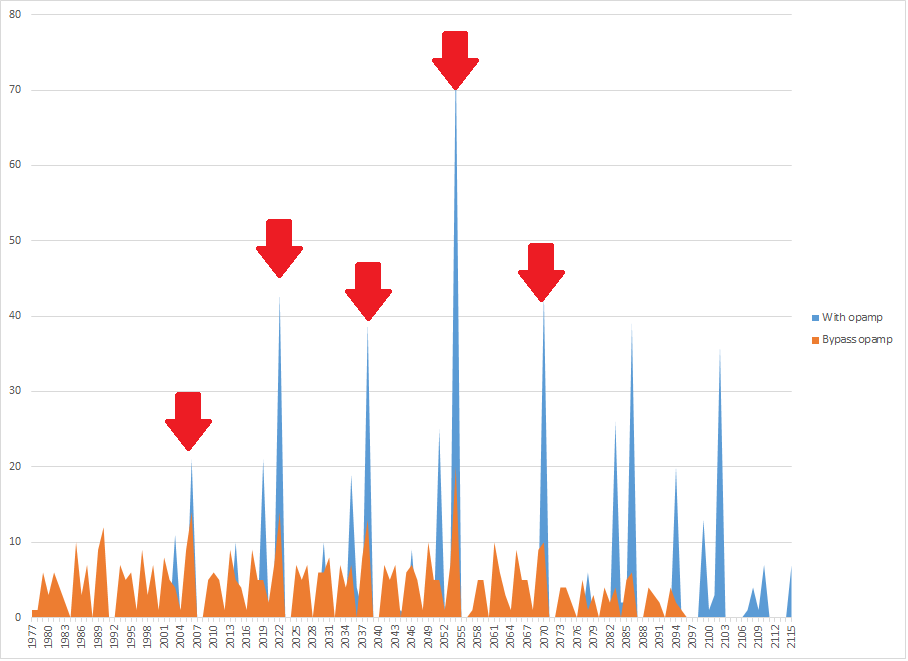

I had a problem in the pas few days with the ADC conversion of the F2837x controlCARD R1.3 and I think we found the source of the problem. Wewere unable to get good conversions with the ADCs. We were always see multiple samples with the same value. By bypassing all the op amp (U13 OPA4350) of the 3.0V voltage reference (U12 REF5030) the conversion results seem to are very good. Could you please confirm that the problem come from the op amp on the devboard. Also could you explain why we get this kind of results with the amplifier on the board.

Link to my previous posts:

Regards

Dany