Other Parts Discussed in Thread: SYSBIOS

Hello,

Could you please help our study of the titled point ?

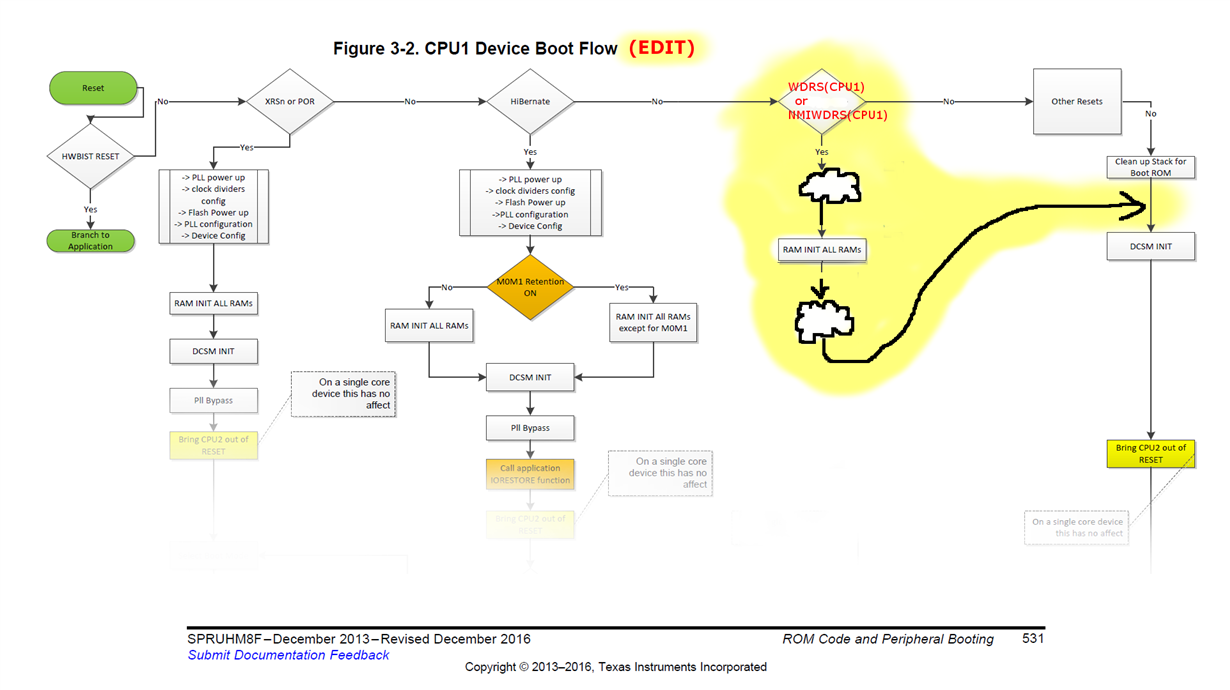

Q1: The TRM, spruhm8f, p531, figure 3-2.

Q1-1: I think that, in fact, the reset causes {WDRS(CPU1) or NMIWDRS(CPU1)} will initialize all the RAM. Is it correct ?

Q1-2: Strictly speaking, I think the figure doesn't show the point above, that is, "{WDRS(CPU1) or NMIWDRS(CPU1)} will initialize all the RAM". Is it correct ?

Q1-3: Are there any RAM resources which are NOT initialized by the {WDRS(CPU1) or NMIWDRS(CPU1)} ? My customer is looking for that.

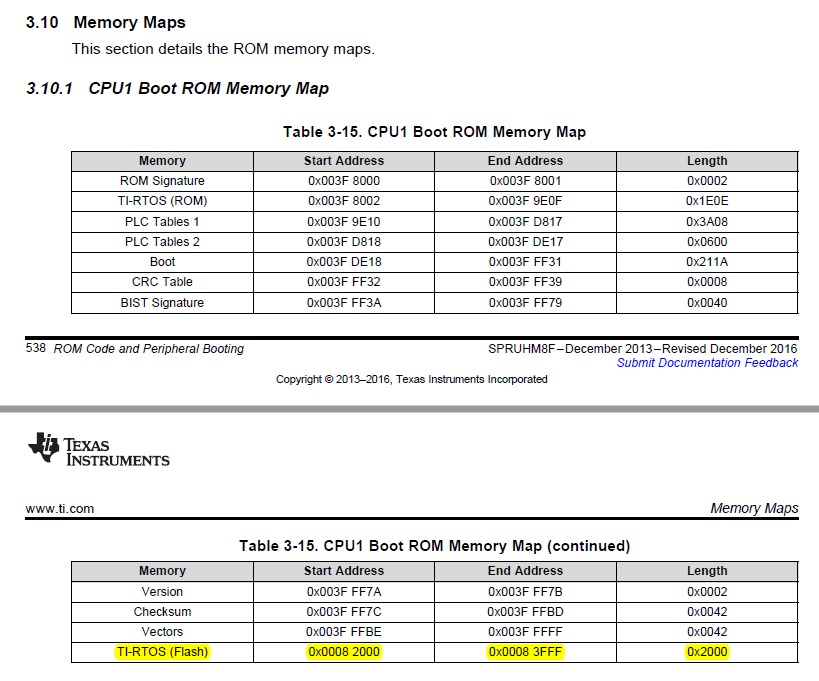

Q2: The TRM, spruhm8f, p538, Table 3-15.

Could you please tell me why this address, was reserved for TI-RTOS(Flash) ? The address is necessary for any reason ? Like an entry point of some callbacks ?