Part Number: TMS320F28069

Dear All,

My application is Phase shift full bridge topology.

I using the up count for EPWM4A/4B for lead side EPWM6A/6B for lag side.

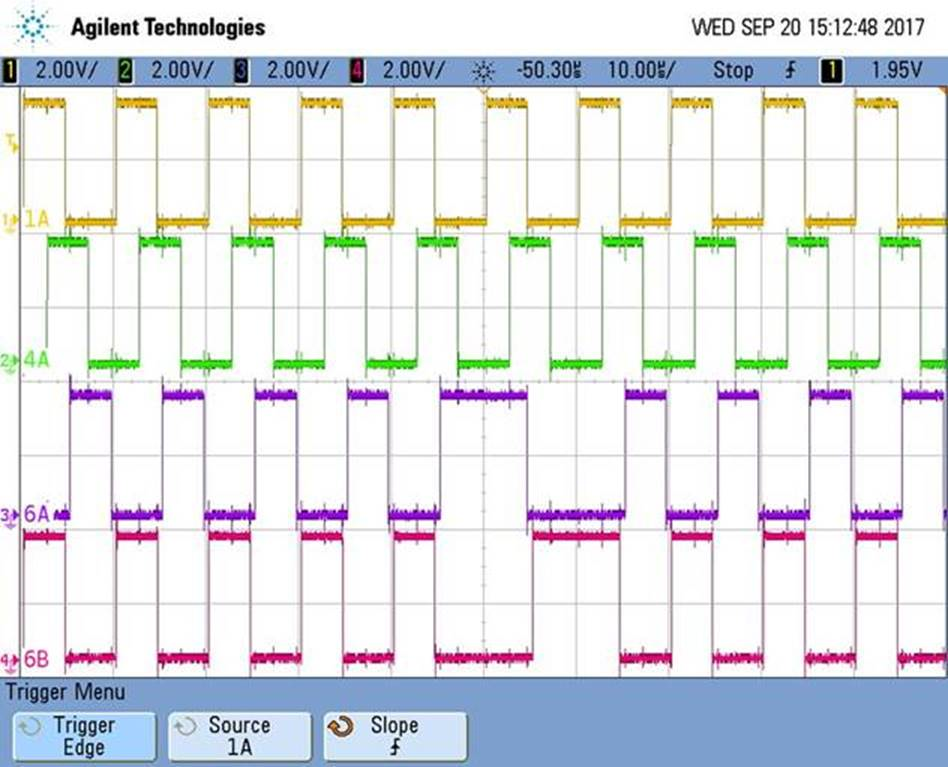

When I changed the TBPHS register from 225 to 675 (PRD 900, CMPA 450 and CMPB 400).

There will happen one switching cycle the DPWM long extension.

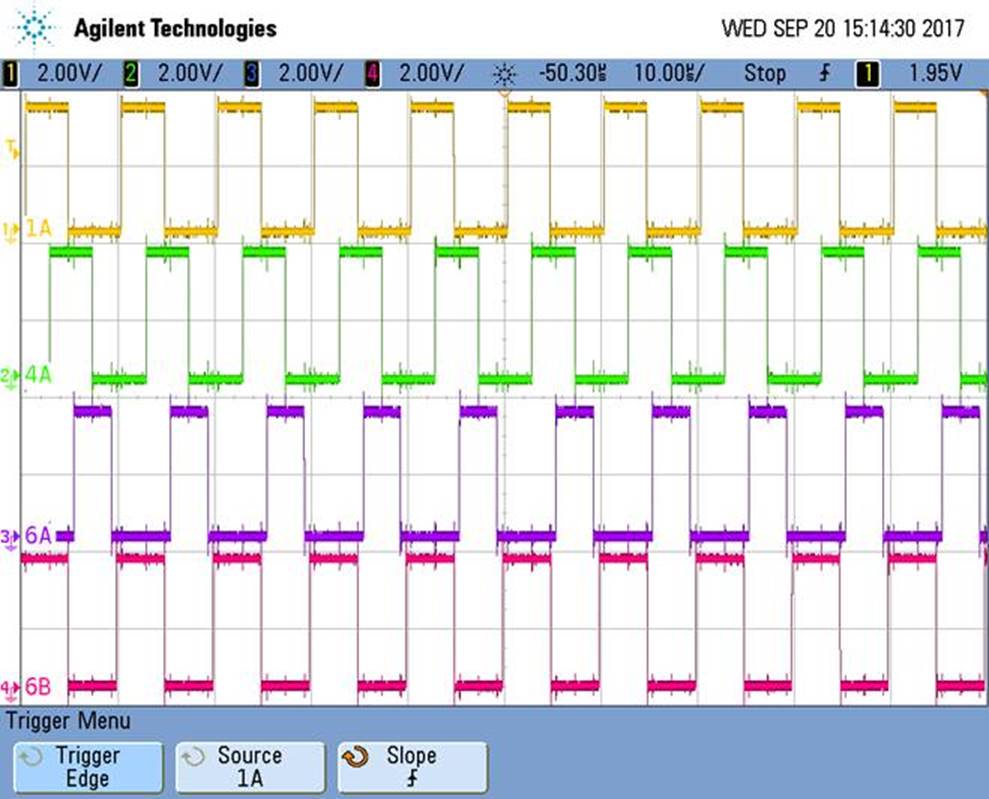

My solution is clear the CBU of AQCTLA from 0 to 1 it can fix the long pulse problem.

Is is has chance to miss the edge during TBPHS update?

//EPwm6Regs.AQCTLA.bit.rsvd = 0 ;//bit 15 14 13 12

EPwm6Regs.AQCTLA.bit.CBD = 0 ;//bit 11 10 //

EPwm6Regs.AQCTLA.bit.CBU = 1 ;//bit 9 8 //

EPwm6Regs.AQCTLA.bit.CAD = 0 ;//bit 7 6 //

EPwm6Regs.AQCTLA.bit.CAU = 1 ;//bit 5 4

EPwm6Regs.AQCTLA.bit.PRD = 0 ;//bit 3 2

EPwm6Regs.AQCTLA.bit.ZRO = 3 ;//bit 1 0

Regards,

Bard