Hi,

a customer has some questions on ADC self calibration.

The question is around the F2806x periodic ADC zero offset self calibration required per errata in http://www.ti.com/lit/er/sprz342k/sprz342k.pdf

They are seeing the offset value change somewhat with temperature, where the test setup is spelled out below. Could you let me know if this temperature dependency is to be expected in the range they are seeing below?

Secondly there is a test below that tries to establish dependency on input resistance of the VREFLO path, but I am not sure if this is a good test, please see below. Again is this something within the range expected?

General Setup:

1. Our system is leveraging the internal voltage reference for the ADC.

2. We leave the VREFHI pin floating.

3. The VREFLO pin is directly shorted to ground.

4. We run the recommended calibration routine using VREFLO as described on spruh18g p. 499.

5. The routine for calibration in use ping-pongs between two sets of 5 ADC reads of VREF0, where the first read is discarded, and the 4th read triggers a request for the next set.

6. A temporary offset of 80 counts is applied and 256 values are accumulated and averaged to find our error.

7. The routine uses ACQPS = 6 (7 cycles) and no overlap mode is enabled.

8. *We found that streaming through 8 channels and preserving the first entry did affect the resulting reading generated.

Test setup for ADC offset dependent on temperature

1. Performing the initialization above sets ADCOFFTRIM to 0x22

2. We re-run calibration and consistently get this value.

3. Reading a 1.65V reference reads 0x0822-0x824 (roughly 1.672V).

4. Nulling the ADCOFFTRIM returns roughly 0x800-0x802

5. Using another channel and some gain circuitry we applied a 18-24V input and noticed the resulting register value align precisely with the expected input if no offset was applied.

6. We took out a heat gun and brought the board temperature up from appx 20C to appx 60C. The voltage range was tested again. We noticed a possible 1 count drift. Nothing significant.

7. We restarted the processor, holding the temperature high. Calibration generates 0x1E

8. We re-run calibration, it maintains the new value at temperature.

9. For each measurement on the ADC, we confirmed the corresponding voltage at the pin with an o-scope with an accuracy of roughly 0.002V

Test setup for ADC offset based on VREFLO input resistance

1. Setting up a new board, I run a baseline check. Calibration yields 0x1C off VREFLO.

2. I apply ground to an external pin (B5) and modify the calibration routine to use the external value. 0x1B

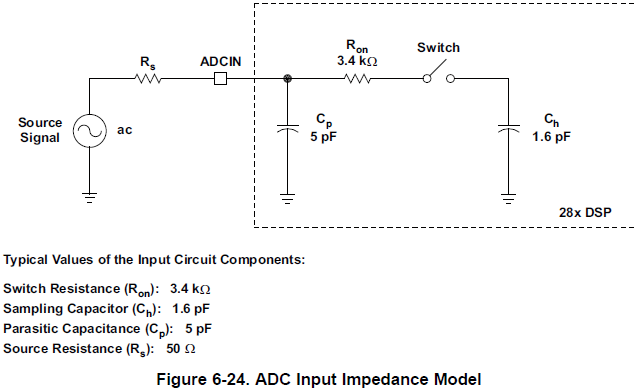

3. I put a 5.9kohm resistor in the way and recalibrate. 0x1D0 (10x the offset).

4. I replace with a 2.2kohm resistor. 0x13A.

5. 220Ohm, 0x1C4, 0x1C3

6. 10Ohm, 0x18, 0x19, 0x19

7. 3.3Ohm, 0x1D (increasing as we approach 0!)

8. Floating, 0x16C, 0x16B, 0x167 (Lower than a 5.9k Resistor!)

Conclusions:

1. There appears to be a strong sensitivity to the input resistance applied to the ADC when a 0V source is applied.

2. The system naturally appears to relax to 0x167, so it would be natural for resistances above a threshold to approach this value.

3. For resistance below 500 ohms, the behavior is non-linear.

4. There is temperature sensitivity in the measurement of a VREFLO.

5. This sensitivity does not appear to affect ADC readings away from the rails, possibly implying gain error or nonlinearity approaching the rails.

6. Unsurprisingly, floating values show greater noise in the resulting calibration.

Could someone comment on the tests and conclusions?

Thanks!

--Gunter