Part Number: TMS320F28377S

Other Parts Discussed in Thread: C2000WARE

hello Community,

What I got:

At the moment I got a working Peak-Current with slope-compensation.

The PWM starts (ON) at the beginning of the PWM-period with a CounterCompare.

The Off-Switching happens when the meausred Signal is same or higher the Comparator-Value. Positive-Pin is the measured external signal and the Negative Pin is feed by DAC-Output. The DAC-Value is configured with the internal Ramp-Generator. (At the Beginning of the PWM-Period is a fine working blanking-window)

Until now the Comparator-Sts is sychron read and feed through x-bar and so into Trip-Zone as a CBC-Event.

I noticed, that my DIGITAL FILTER right after the comparator is not working. I need this Filter to avoid peaks from 2nd switching device.

What I want:

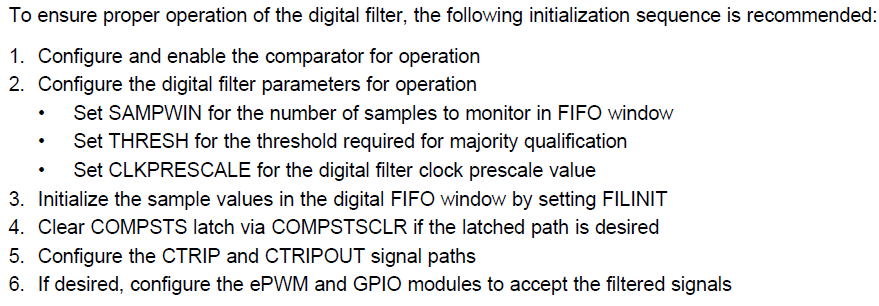

I read, that I have to configure this

Cmpss1Regs.COMPCTL.bit.CTRIPHSEL = CTRIP_SYNCH

to this

Cmpss1Regs.COMPCTL.bit.CTRIPHSEL = CTRIP_FILTER;

or this

Cmpss1Regs.COMPCTL.bit.CTRIPHSEL = CTRIP_LATCH;

to use the right output of the digital Filter.

For some unkown reason the Switching-Off not happen often enough. The picture in this post shows it. Every PWm-Period should the PWM switch off at the same ponit, but nothings happen.

Channel1 (yellow) -PWM2A

Channel3(blue)-The input-Signal for the Comparator

Channel4(green)-PWM7A -shows the Beginnning of a new PWM-period and covers the on the ON-Time the Blanking-Window

After The Green-PWM rises the DAC produces 3,3V-Output and this falls until a new PWM-period stars to 1,66V

Here I put the relevant Code:

Cmpss1Regs.COMPCTL.bit.COMPDACE = 1;

Cmpss1Regs.COMPCTL.bit.COMPHSOURCE = NEGIN_DAC;

Cmpss1Regs.COMPDACCTL.bit.SELREF = REFERENCE_VDDA;

Cmpss1Regs.COMPCTL.bit.CTRIPHSEL = CTRIP_FILTER;

Cmpss1Regs.CTRIPHFILCTL.bit.FILINIT=1;//Aktivierung des zusätzlichen Filters

Cmpss1Regs.CTRIPHFILCTL.bit.SAMPWIN=15; //Es müssen 6 Samples +Sample high sein zum Durschalten

Cmpss1Regs.CTRIPHFILCTL.bit.THRESH=10; //Die Mehrheit also 4-Abtasttung müssen wenigstens high sein

Cmpss1Regs.CTRIPHFILCLKCTL.bit.CLKPRESCALE=0; //2-->es wird nur jede zweite Periode ein Sample generriert (system clk)

Cmpss1Regs.COMPSTSCLR.bit.HLATCHCLR=1;//HSYNCCLREN=1;//jeder PWMSYNC will reset latch

Cmpss1Regs.COMPSTSCLR.bit.HSYNCCLREN=1;

Cmpss1Regs.RAMPMAXREFS=65535;//2048; //Shadow-Register für die maximale Rampe -->Regelung -->Einstellung für 15A bei 00A-30A möglicher Strom

Cmpss1Regs.RAMPMAXREFA=65535;//2048; //maximaler Rampen-Wert Startwert

Cmpss1Regs.RAMPDECVALA=33; //in 2000 Schritten müssten nur 2048 Stufen herunter gezählt werden -->Rampe so -15A

Cmpss1Regs.RAMPDECVALS=33;//Shadow-Register

//configuration in ePWM

EPwm2Regs.TZDCSEL.bit.DCBEVT2 = TZ_DCBH_HI; //CBC-Event wird ausgelöst, wenn Comparator B high (1) ist

EPwm2Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 3; //Trip 4 wird in das Digital-Compare-Modul geladen

EPwm2Regs.TZSEL.bit.DCBEVT2 = 1; //CBC-Event wird bei einem Signal vom Komparator (außerhalb des Filters) gesetzt

EPwm2Regs.DCBCTL.bit.EVT2SRCSEL = 1; //CBC-Events werden im digitalen Filter vorgefiltert

EPwm2Regs.DCBCTL.bit.EVT2FRCSYNCSEL = DC_EVT_SYNC; //CBC-Events werden synchron erezugt zur TBCLK

EPwm2Regs.HRPCTL.bit.PWMSYNCSEL=0; //PWMSYNC = CNT_zero signal pulse

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1;

I hope Somebody can help me.

Regards Basti