Other Parts Discussed in Thread: CONTROLSUITE, SFRA, C2000WARE

Tool/software: Code Composer Studio

Dear Concerns / E2E community members,

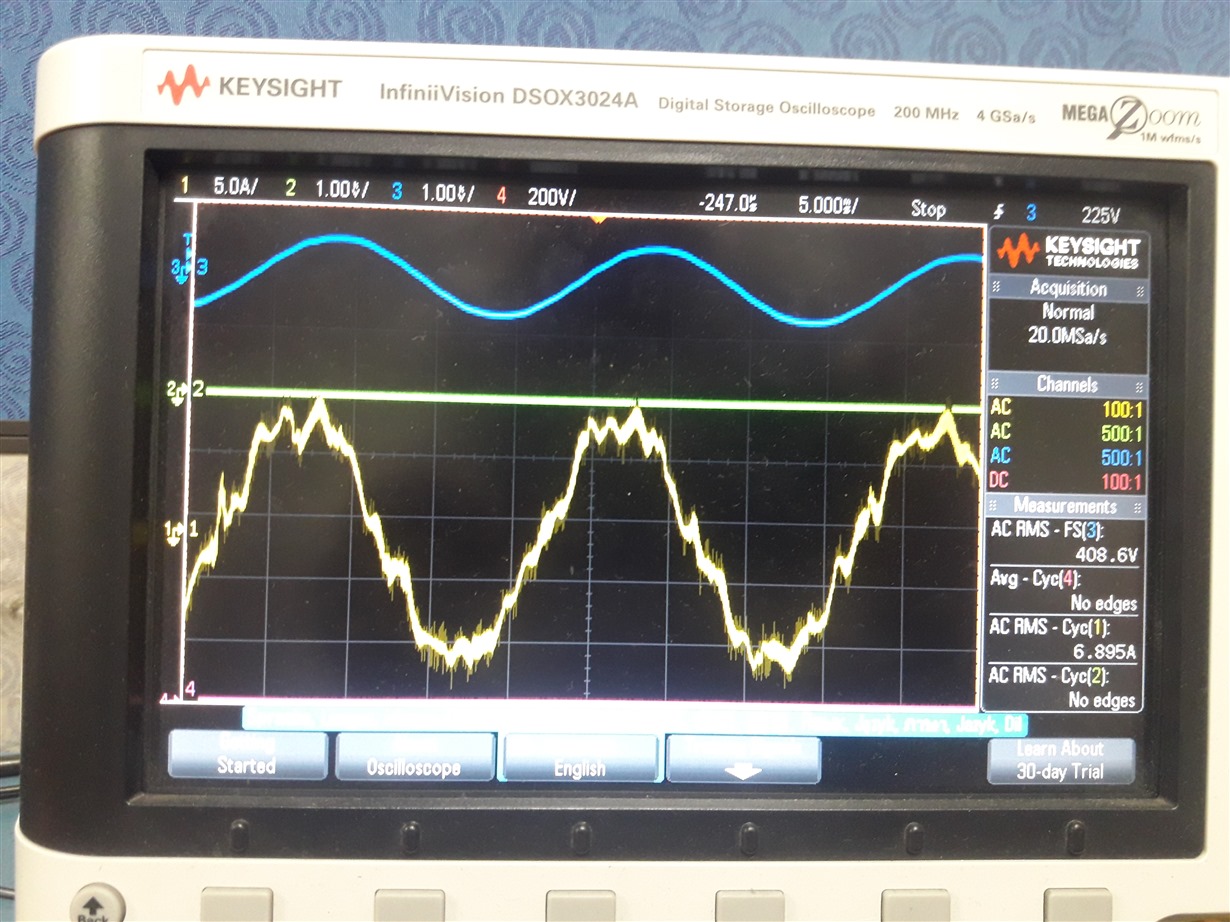

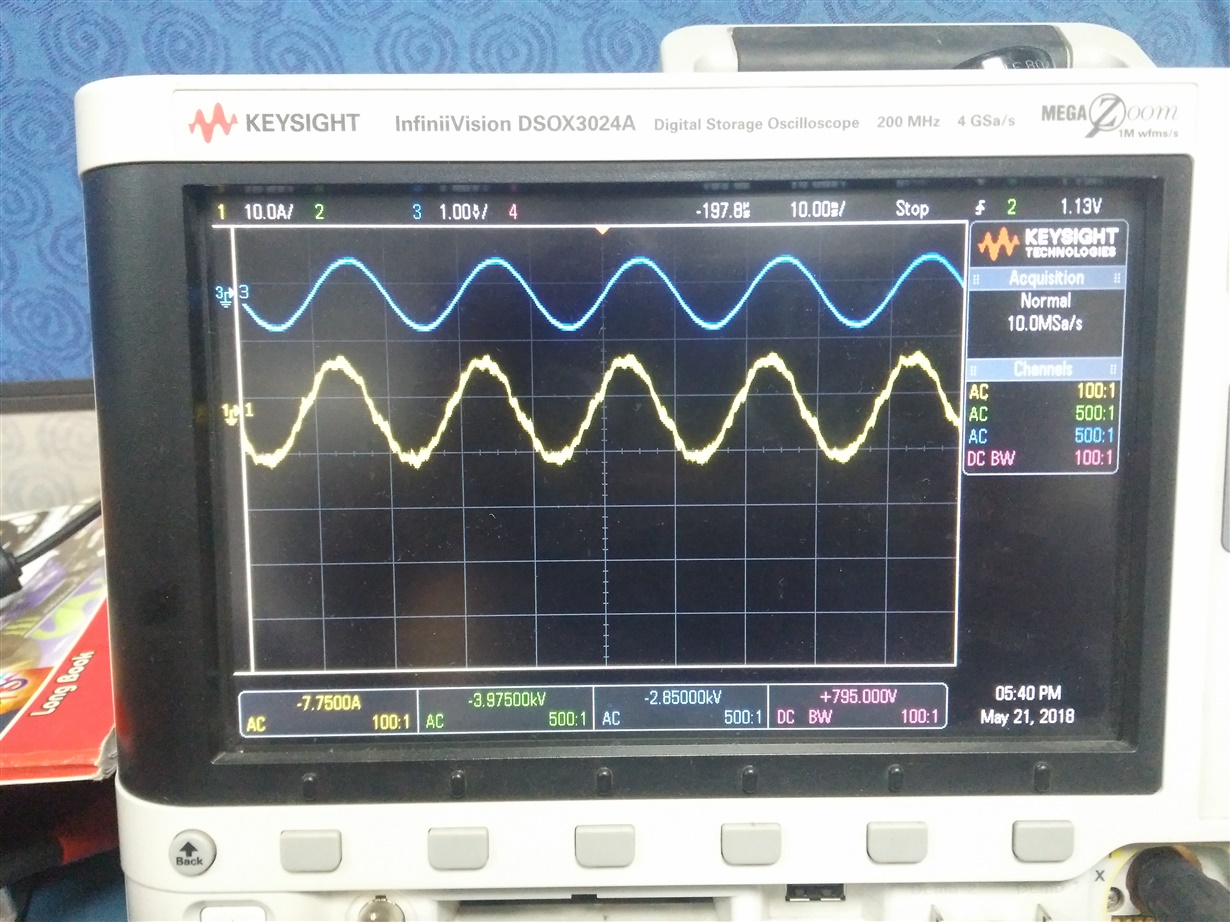

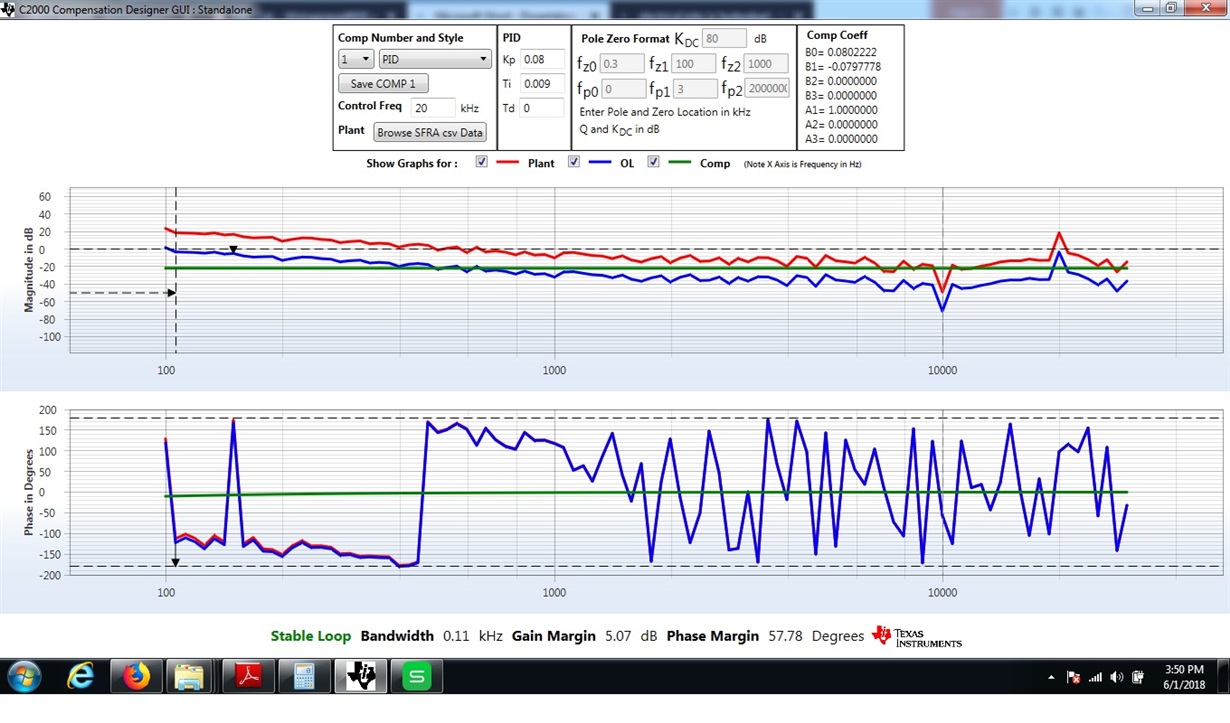

We found current harmonic distortion around 5% and current wave form in yellow colour is attached for your reference . Kindly suggest to improve further.