Other Parts Discussed in Thread: AMC1303M2520,

Hello, everyone

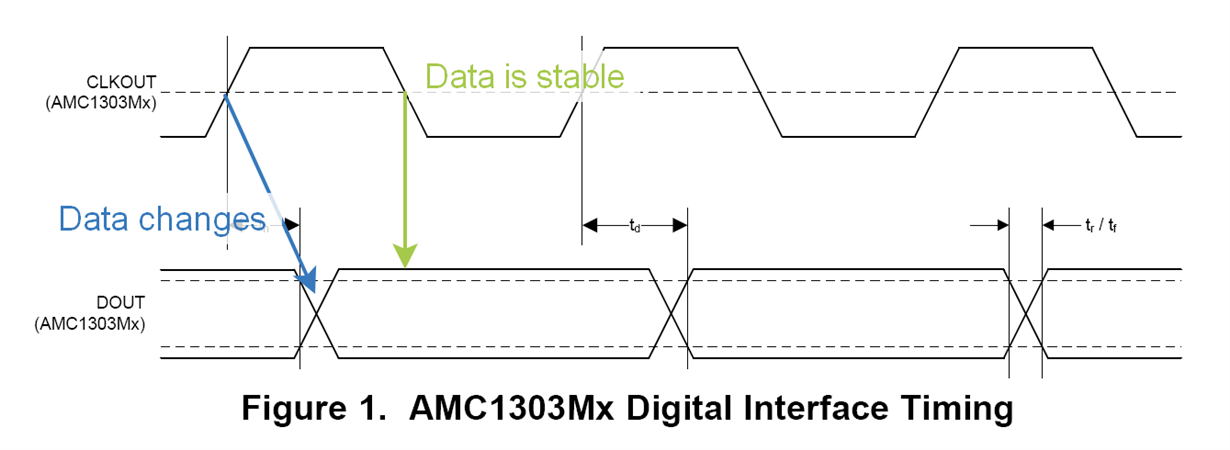

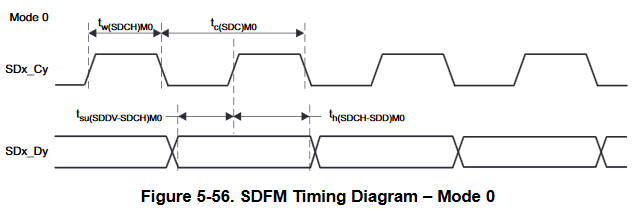

We have a question related to interfacing Sigma-Delta Modulator AMC1303M2520 with SD Filter on F2837xD. The problem is in AMC data hold and delay time after rising edge of CLKOUT: the datasheet says, that data is held for at least 7 ns, and then changed not more than 15 ns later. The MCU latches data at rising edge of CLKOUT.

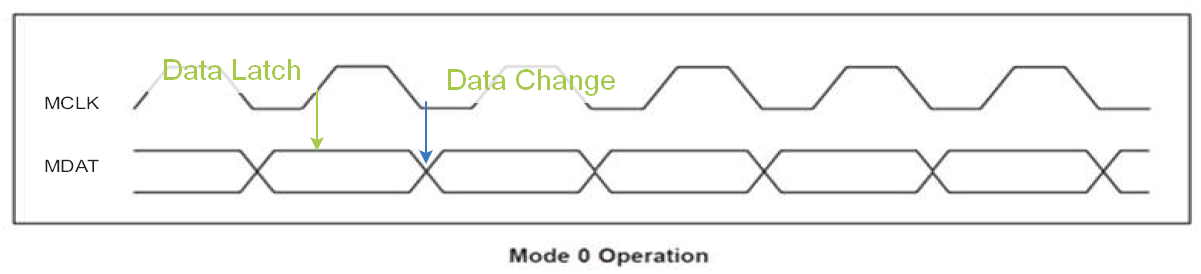

In common cases if data changes with the rising edge, then it sould be read with the falling edge and vice versa. Otherwise there is a possibility of MCU captures wrong data.

Do I have to invert CLKOUT of the AMC1303 in this case to improve reliability?