Hi

I'm testing Comparator Ramp generator features for peak current control implementation.

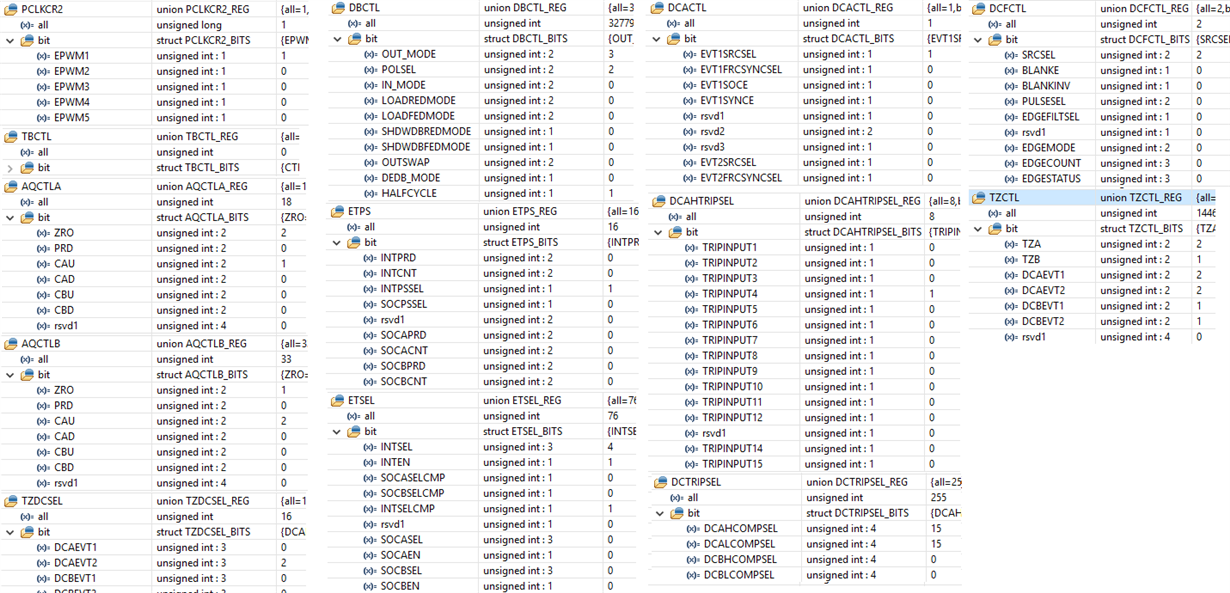

In the program, I use CMPSS1P to compare to ramp value. The result(CMPSS1.CTRIPH) is used

as a DC trip event (cycle-by-cycle) to trip PWM1A to high impedance in the remain part

of the current PWM period.

I found some features are different from what I imaged:

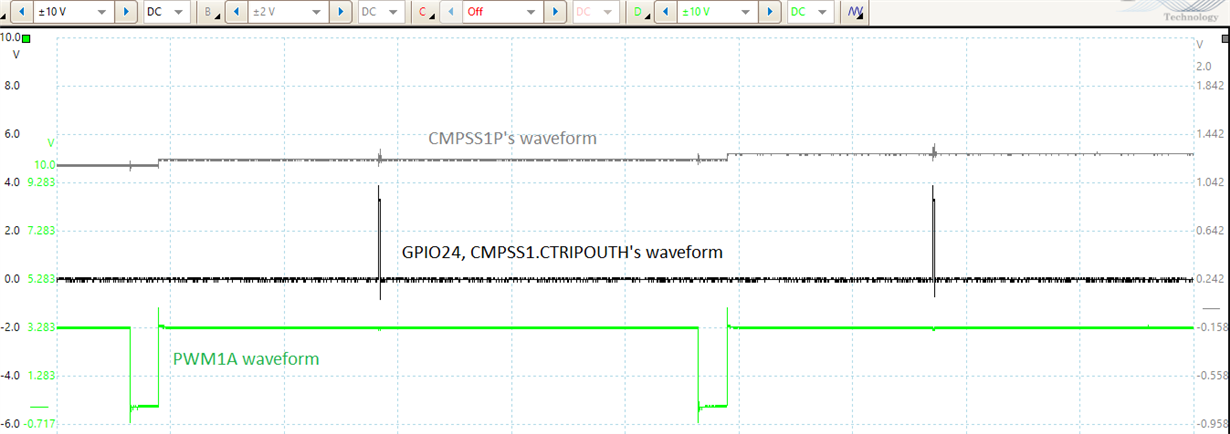

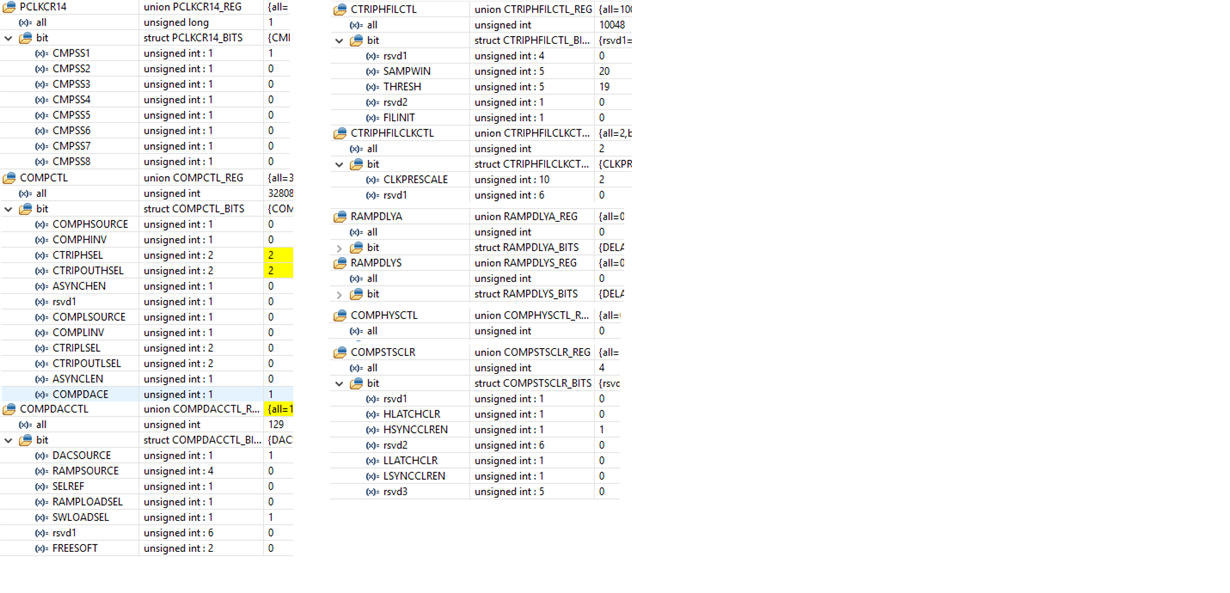

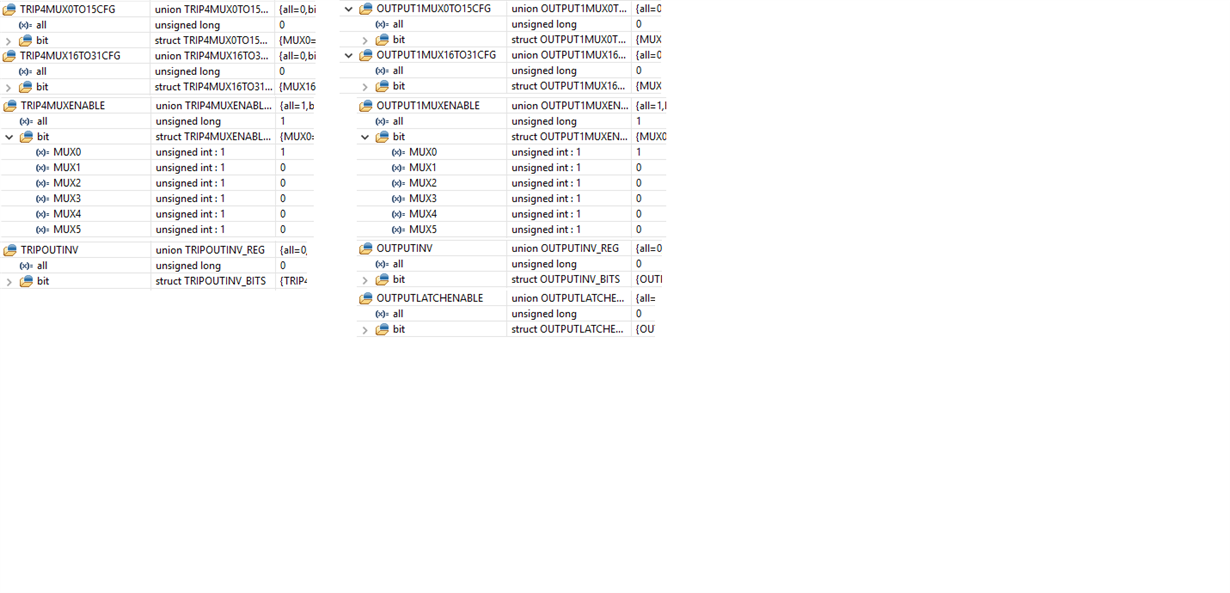

1. I set CMPSS1.COMPCTL[CTRIPHSEL]and CMPSS1.COMPCTL[CTRIPOUTHSEL] to 2, so COMPSTS[COMPHSTS]

will be sent to PWM X-Bar, it will be sent to Output X-Bar (GPIO24) to check this signal.

I think COMPSTS[COMPHSTS] will remain high in a PWM period whenever it becomes high, but when

I check GPIO24, it will become high in a short time then remain low in the subsequent part

of the PWM period. Please see the waveforms below.

My question is why COMPSTS[COMPHSTS] goes low after it becomes high? Do I have any way to

keep COMPSTS[COMPHSTS] high in the remain part of PWM period (except using latched value)?

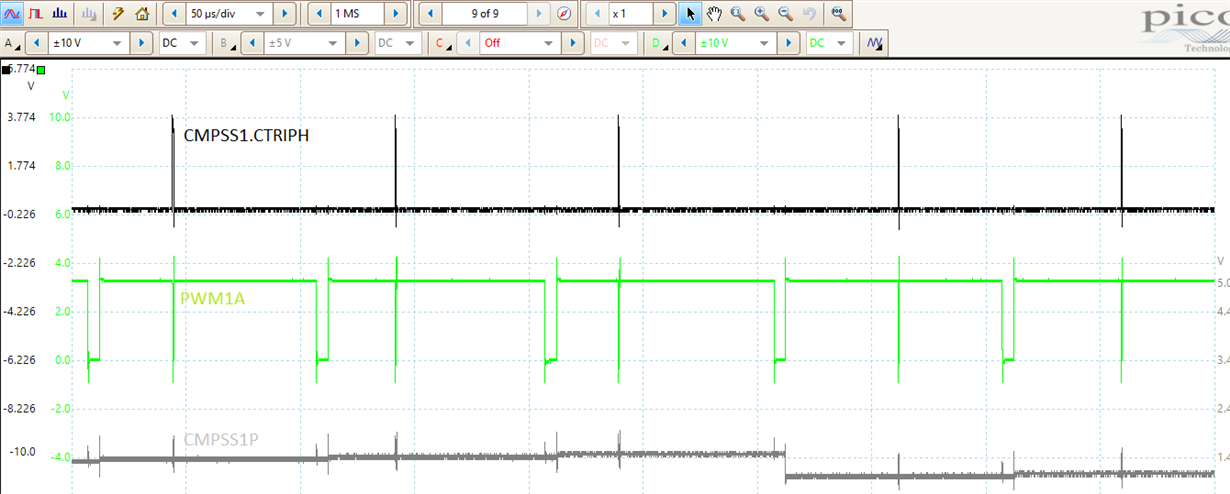

2. I think in a PWM cycle-by-cycle trip control, when a trip event becomes active, PWM output

will take trip action until the end of the current PWM period. But from above waveforms,

PWM output is only tripped when COMPSTS[COMPHSTS] becomes high and it resumes to normal mode in the

subsequent time of the current PWM period. This is different to type 2 PWM. Do I have any way

to remain trip action at the subsequent time of the current PWM period?

The project is attached for your review.

thanks,

Jiakai