Hello everyone,

I want to use both cores to control different stages of a converter and I'm wondering a few things:

- I remember reading something about ADC result registers having mirrors in both cores. Can someone confirm that both cores have independent access to the ADC Result Regs? Is there any risk of delay if both cores try to read them at the same time, like a round-robin scheme or such?

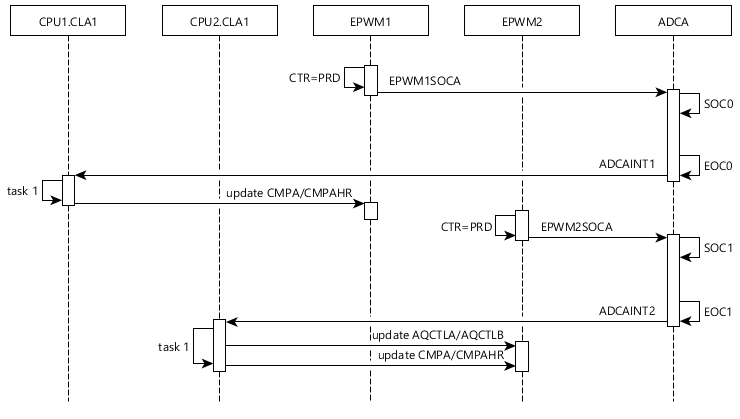

- I found a few topics stating that CPU2 cannot be used to clock or configure the HRPWM modules. Is it possible nonetheless to configure EPWM + HRPWM on CPU1 and then have CPU2.CLA1 update CMPA/CMPAHR?

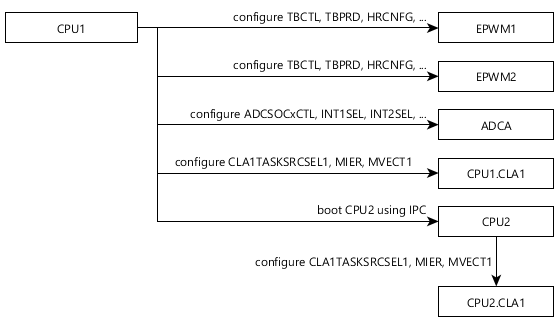

The initialization of the F28379D would go like so:

For the realtime control architecture I would like to achieve what is described in the following diagram.

Is it possible and if not what is the recommended way to do something similar? I thought about only performing calculations in CPU2.CLA1 and passing back to CPU1 the values to write to the EPWM, but I'd rather avoid the overhead.

Cheers,

Pierre