Other Parts Discussed in Thread: MOTORWARE

I am writing some code to interact with a external peripheral that uses a SPI-like communication. I give it a clock and it gives me data, so I'm using the peripheral as follows:

- Read the data in the SPI's RX FIFO

- Process data

- Fill Tx FIFO

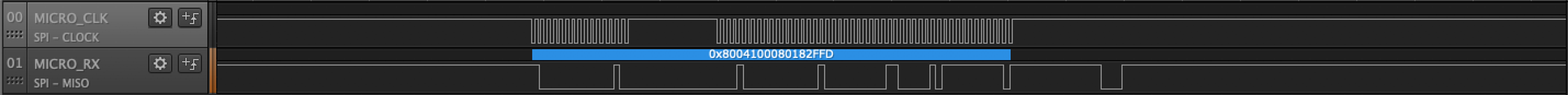

This routine runs at 1khz in the SYS-BIOS. The problem is I run into traces that look like this:

The gap on the top(CLK) trace causes the peripheral to time out and think that the next word is a new transaction.

This is what the code for filling the TX FIFO looks like:

// Fill the FIFO to get new sample ready.

for (int words_needed = 4; words_needed > 0; words_needed--) {

spi_handle_->SPITXBUF = 0xFFFF;

// Wait for buffer to empty

while (SPI_getTxBufferStatus(spi_handle_) == SPI_TxBufferStatus_Full);

}

This isn't atomic, so when interrupted, this filling process can be delayed. What I want to do is put a SPI_disableTx() before then SPI_enableTx() after, but for some reason when you disable TX it doesn't stop the peripheral from clocking which ruins this idea.

Would love some help on this!

Thanks!