Other Parts Discussed in Thread: ADS7254

Dear sir/Madam,

I am using ads7254 external ADC with LaunchPad TMS320F28379D using SPI. I have tried the loopback example and works correctly. but when I load configuration with ADC, I read "0" in "SpiaRegs.SPIRXBUF" register. The DSP is in master mode, SPI clock is 500KHz.

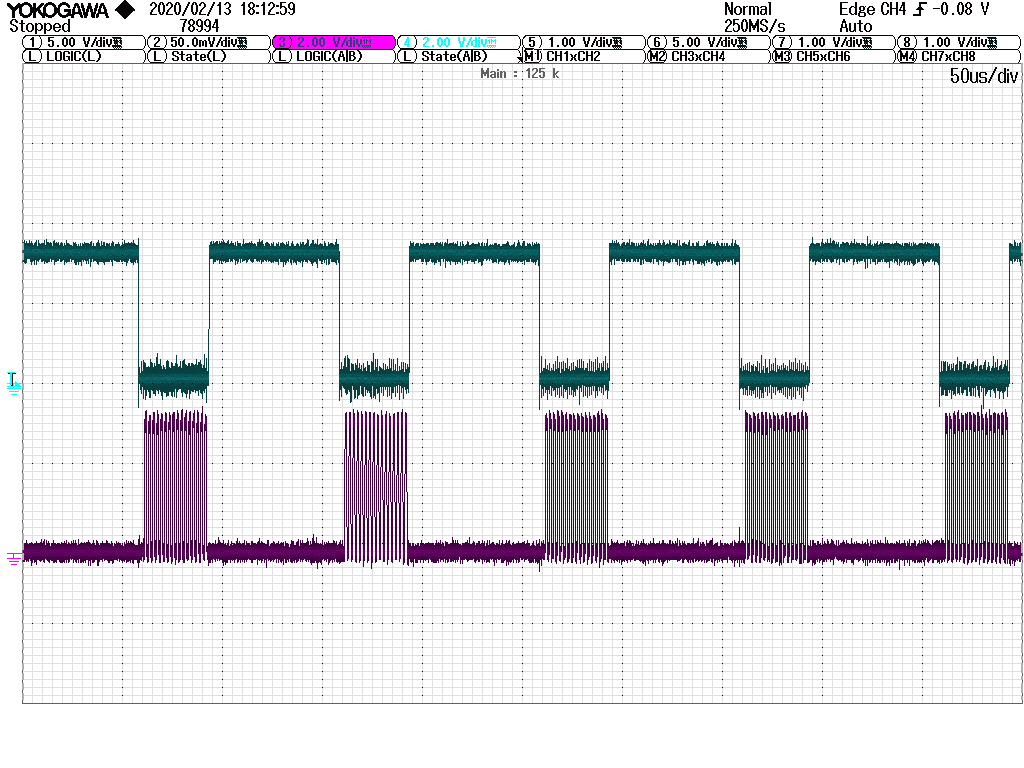

I am not receiving anything on SPISOMI, I read 0 always, whenever there is clock. When clock is not present it goes high. Also, there is delay between two SPI channels, which I do not understand why ?

I attach below the SPI configuration. I have also tried to send to ADC 0x0800 instead of 0x8800, as I want to work in 16-CLK, Dual-SDO Mode (CFR.B11 = 1, CFR.B10 = 0),but I read 0 all the time.

Thank you.

#define SPI_BRR ((200E6 / 4) / 500E3) - 1

//============== SPI - A ======================

//===============================================

//Init GPIO SPIA

EALLOW ;

GpioCtrlRegs.GPBPUD.bit.GPIO58 = 0; // Enable pull-up on GPIO16

GpioCtrlRegs.GPBPUD.bit.GPIO59 = 0; // Enable pull-up on GPIO17

GpioCtrlRegs.GPBPUD.bit.GPIO60 = 0; // Enable pull-up on GPIO18

GpioCtrlRegs.GPBPUD.bit.GPIO61 = 0; // Enable pull-up on GPIO19

GpioCtrlRegs.GPBQSEL2.bit.GPIO58 = 3;

GpioCtrlRegs.GPBQSEL2.bit.GPIO59 = 3; // Asynch input GPIO17

GpioCtrlRegs.GPBQSEL2.bit.GPIO60 = 3; // Asynch input GPIO18

GpioCtrlRegs.GPBQSEL2.bit.GPIO61 = 3; // Asynch input GPIO19

GpioCtrlRegs.GPBGMUX2.bit.GPIO58 = 3; // Configure GPIO16 as SPI

GpioCtrlRegs.GPBGMUX2.bit.GPIO59 = 3;

GpioCtrlRegs.GPBGMUX2.bit.GPIO60 = 3;

GpioCtrlRegs.GPBGMUX2.bit.GPIO61 = 3;

GpioCtrlRegs.GPBMUX2.bit.GPIO58 = 3;

GpioCtrlRegs.GPBMUX2.bit.GPIO59 = 3; // Configure GPIO17 as SPI

GpioCtrlRegs.GPBMUX2.bit.GPIO60 = 3; // Configure GPIO18 as SPI

GpioCtrlRegs.GPBMUX2.bit.GPIO61 = 3; // Configure GPIO19 as SPI

GpioCtrlRegs.GPBDIR.bit.GPIO58 = 1;

GpioCtrlRegs.GPBDIR.bit.GPIO59 = 0;

GpioCtrlRegs.GPBDIR.bit.GPIO60 = 1;

GpioCtrlRegs.GPBDIR.bit.GPIO61 = 1;

//============== SPI - B ======================

//========== Init GPIO SPIB ================

GpioCtrlRegs.GPAPUD.bit.GPIO24 = 0; // Enable pull-up on GPIO24

GpioCtrlRegs.GPAPUD.bit.GPIO25 = 0; // Enable pull-up on GPIO25

GpioCtrlRegs.GPAPUD.bit.GPIO26 = 0; // Enable pull-up on GPIO26

GpioCtrlRegs.GPAPUD.bit.GPIO27 = 0; // Enable pull-up on GPIO27

GpioCtrlRegs.GPAQSEL2.bit.GPIO24 = 3; // Asynch input GPIO24

GpioCtrlRegs.GPAQSEL2.bit.GPIO25 = 3; // Asynch input GPIO25

GpioCtrlRegs.GPAQSEL2.bit.GPIO26 = 3; // Asynch input GPIO26

GpioCtrlRegs.GPAQSEL2.bit.GPIO27 = 3; // Asynch input GPIO27

GpioCtrlRegs.GPAGMUX2.bit.GPIO24 = 1; // Configure GPIO24

GpioCtrlRegs.GPAGMUX2.bit.GPIO25 = 1;

GpioCtrlRegs.GPAGMUX2.bit.GPIO26 = 1;

GpioCtrlRegs.GPAGMUX2.bit.GPIO27 = 1;

GpioCtrlRegs.GPAMUX2.bit.GPIO24 = 2; //as SPI

GpioCtrlRegs.GPAMUX2.bit.GPIO25 = 2; // Configure GPIO25 as SPI

GpioCtrlRegs.GPAMUX2.bit.GPIO26 = 2; // Configure GPIO26 as SPI

GpioCtrlRegs.GPAMUX2.bit.GPIO27 = 2; // Configure GPIO27 as SPI

GpioCtrlRegs.GPADIR.bit.GPIO24 = 1;

GpioCtrlRegs.GPADIR.bit.GPIO25 = 0;

GpioCtrlRegs.GPADIR.bit.GPIO26 = 1;

GpioCtrlRegs.GPADIR.bit.GPIO27 = 1;

EDIS;

void spi_init(){

//Init SPI A

SpiaRegs.SPICCR.bit.SPISWRESET=0;

SpiaRegs.SPICCR.bit.CLKPOLARITY=0; //Output Rising Edge, Input is latched Falling Edge

SpiaRegs.SPICCR.bit.HS_MODE =0; // High Speed Mode DISABLE

SpiaRegs.SPICCR.bit.SPICHAR=15;

SpiaRegs.SPICCR.bit.SPILBK=0; //Loopback Disable (Testing Mode)

SpiaRegs.SPICTL.bit.MASTER_SLAVE = 1;

SpiaRegs.SPICTL.bit.TALK = 1;

SpiaRegs.SPICTL.bit.CLK_PHASE = 0;

SpiaRegs.SPICTL.bit.SPIINTENA = 0;

SpiaRegs.SPIBRR.bit.SPI_BIT_RATE=SPI_BRR ;

SpiaRegs.SPICCR.bit.SPISWRESET=1;

//Init SPI B

SpibRegs.SPICCR.bit.SPISWRESET=0;

SpibRegs.SPICCR.bit.CLKPOLARITY=0; //Output Rising Edge, Input is latched Falling Edge

SpibRegs.SPICCR.bit.HS_MODE =0; // High Speed Mode DISABLE

SpibRegs.SPICCR.bit.SPICHAR=15;

SpibRegs.SPICCR.bit.SPILBK=0; //Loopback Disable (Testing Mode)

SpibRegs.SPICTL.bit.MASTER_SLAVE = 1;

SpibRegs.SPICTL.bit.TALK = 1;

SpibRegs.SPICTL.bit.CLK_PHASE = 0;

SpibRegs.SPICTL.bit.SPIINTENA = 0;

SpibRegs.SPIBRR.bit.SPI_BIT_RATE=SPI_BRR ;

SpibRegs.SPICCR.bit.SPISWRESET=1;

}

__interrupt void epwm1_isr(void)

{

SpiaRegs.SPITXBUF = 0x8800 ;

SpibRegs.SPITXBUF = 0x8800 ;

while (! SpiaRegs.SPISTS.bit.INT_FLAG ) {}

SPI_I_A = SpiaRegs.SPIRXBUF;

while (! SpibRegs.SPISTS.bit.INT_FLAG ) {}

SPI_I_B = SpibRegs.SPIRXBUF;

}