Hi Team,

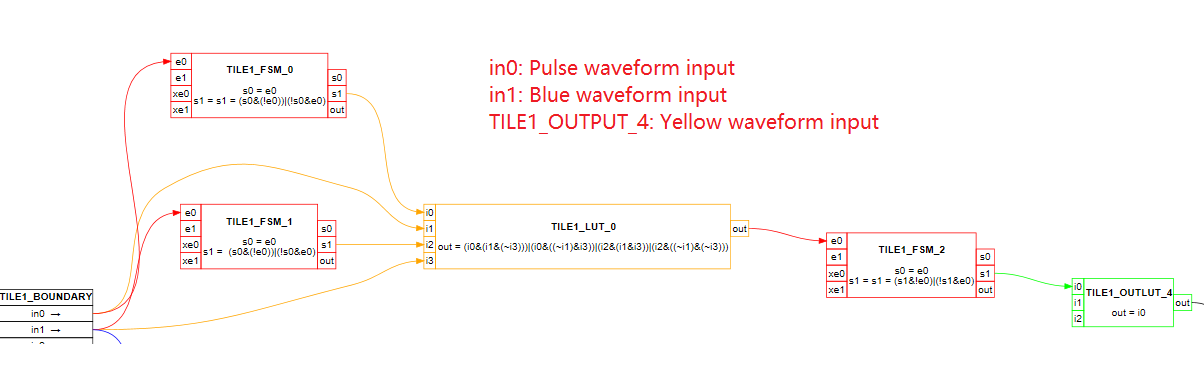

My customer use CLB to implement logic function. they face an strange issue that the CLB output is not correct in real application system while the simulation show that the logic calculation are correct, and in F280049 launchpad do the similar thing can not reproduce this issue. the configuration block is showed as below:

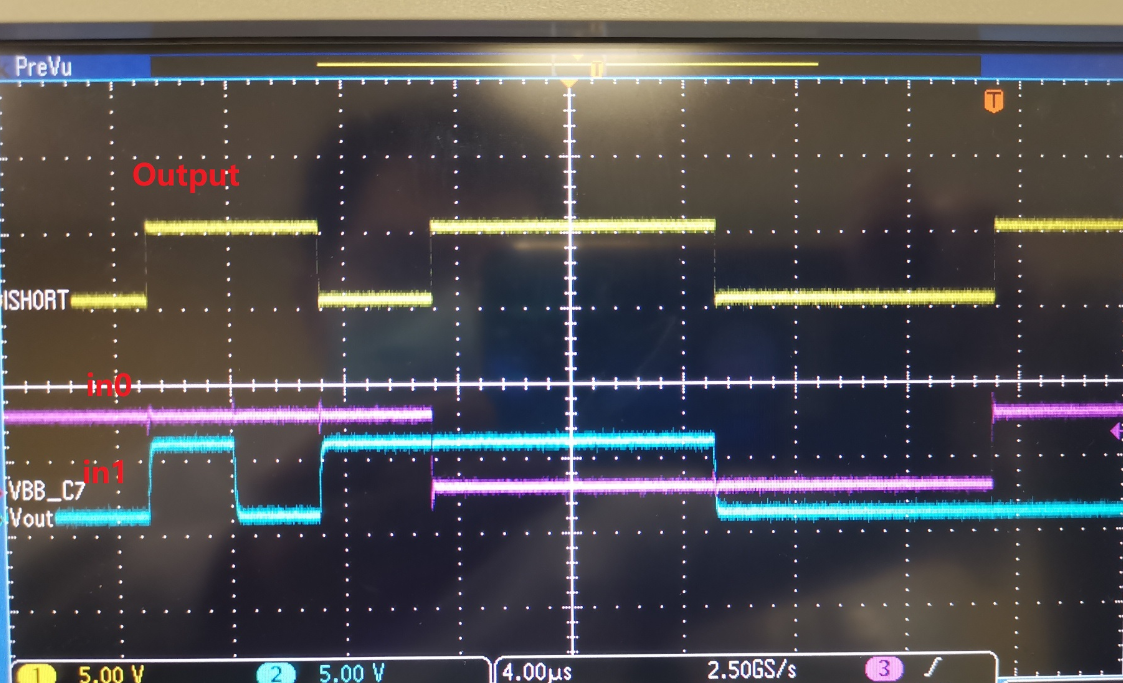

so the waveform of input and output should be like as below, which I did with F280049 launchpad: The waveform below are exactly what we want and are correct.

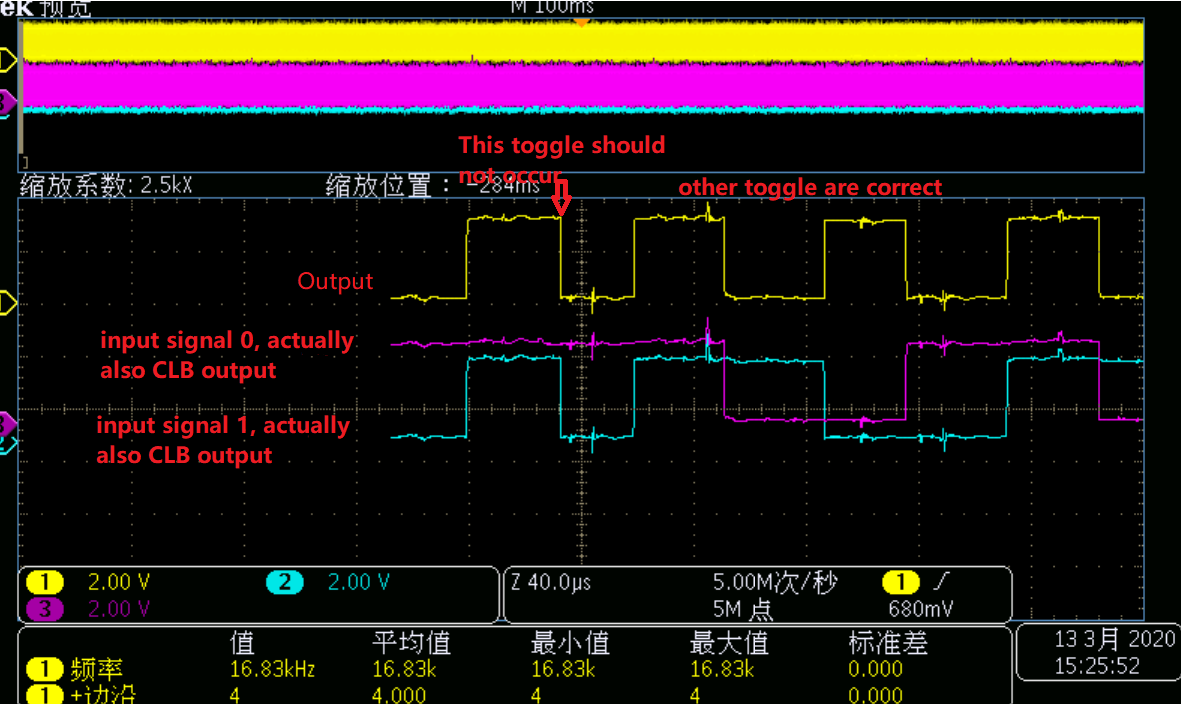

But in customer's system, the two input of the waveform are from their motor encoder signal, in this case, there have issue and sometimes output is wrong. in order to see if any noise of the two input, actually they use two CLB output to show the input signal, we can see that these signal that go to CLB module are clean, in most case the output are correct, but unfortunately sometimes the output is wrong as show in red arrow. we did not know why.

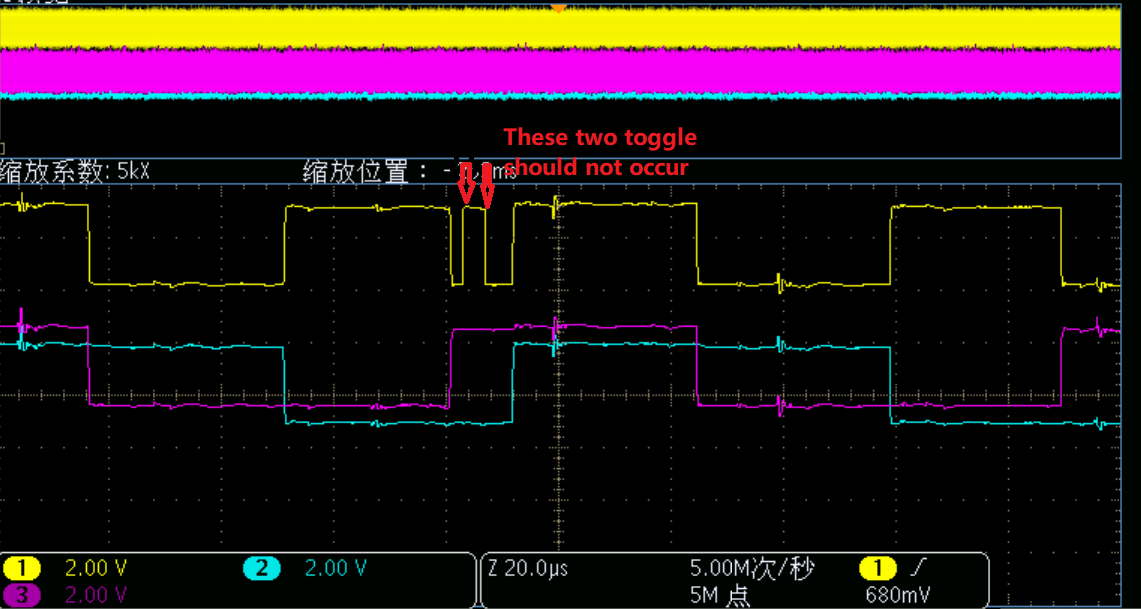

Further more, we also found more strange waveform that are output as below, we think there may have some noise that influence the output, and try to add logic filter that configured by CLB to filtering the input two signals, but it did not work and remain have the issue.

any suggestion on how to fix this issue? Thanks.