Other Parts Discussed in Thread: C2000WARE, TMDXIDDK379D

Hi Champs,

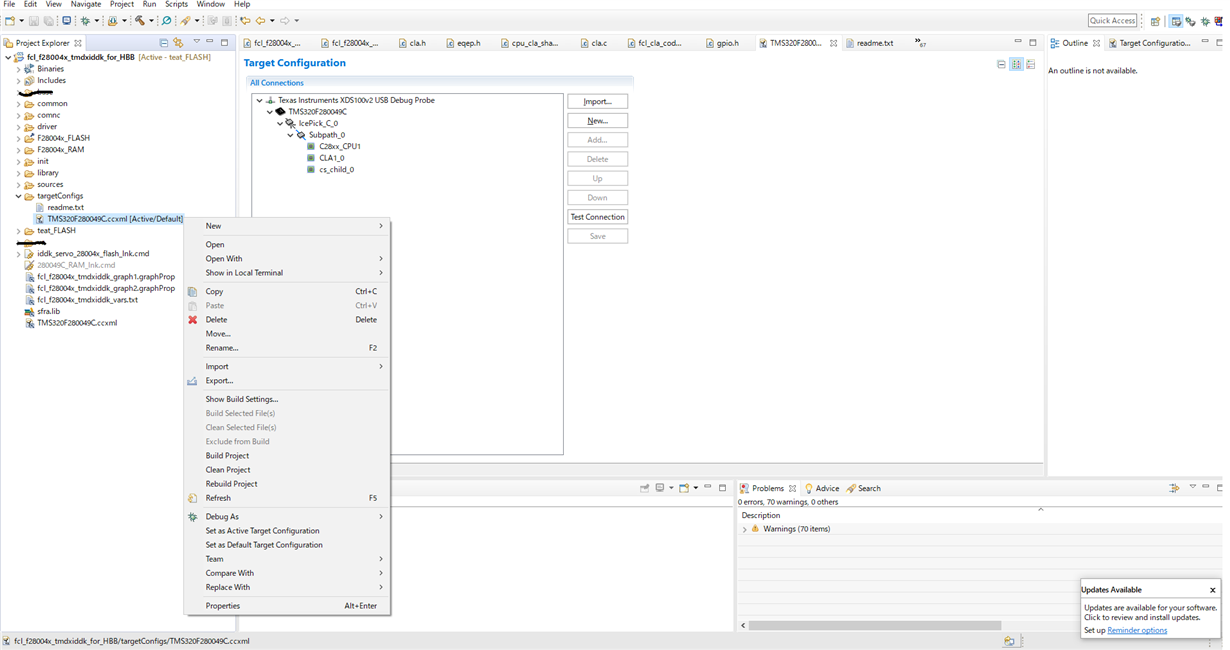

A customer has been facing a problem that the program does not work with a linked command file named “iddk_servo_2837x_flash_lnk_cpu1.cmd” as attached.

The file was modified by the customer.

They have confirmed that the LED sample code works with "28004x_generic_flash_lnk.cmd" with no problem.

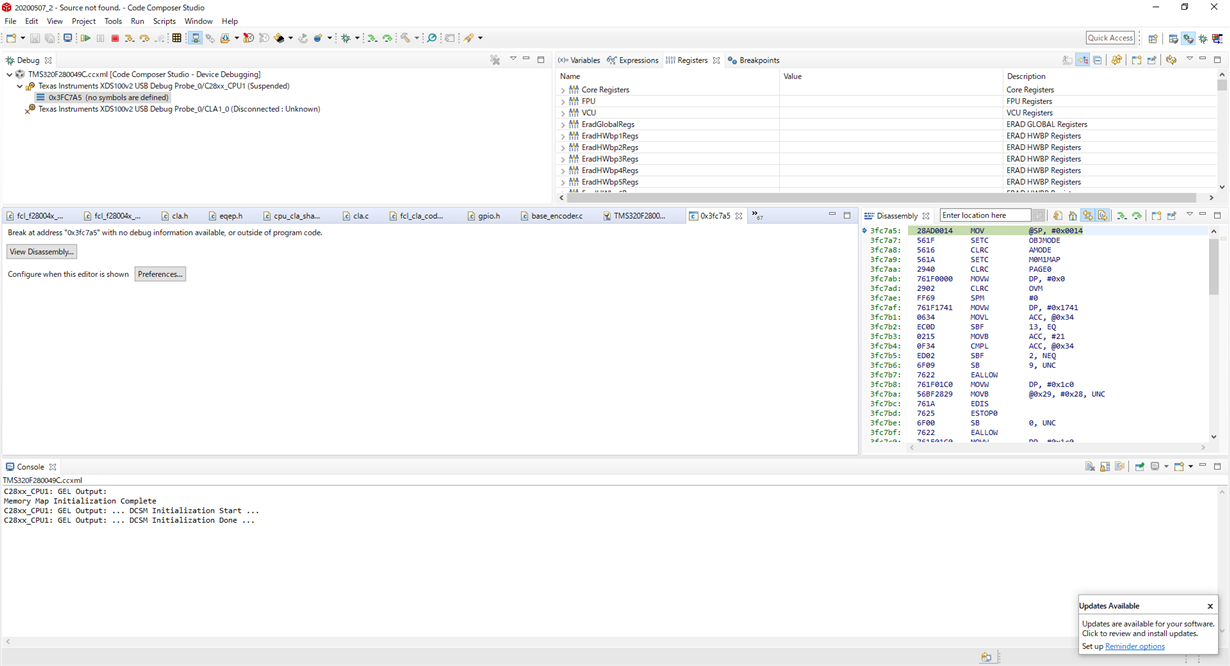

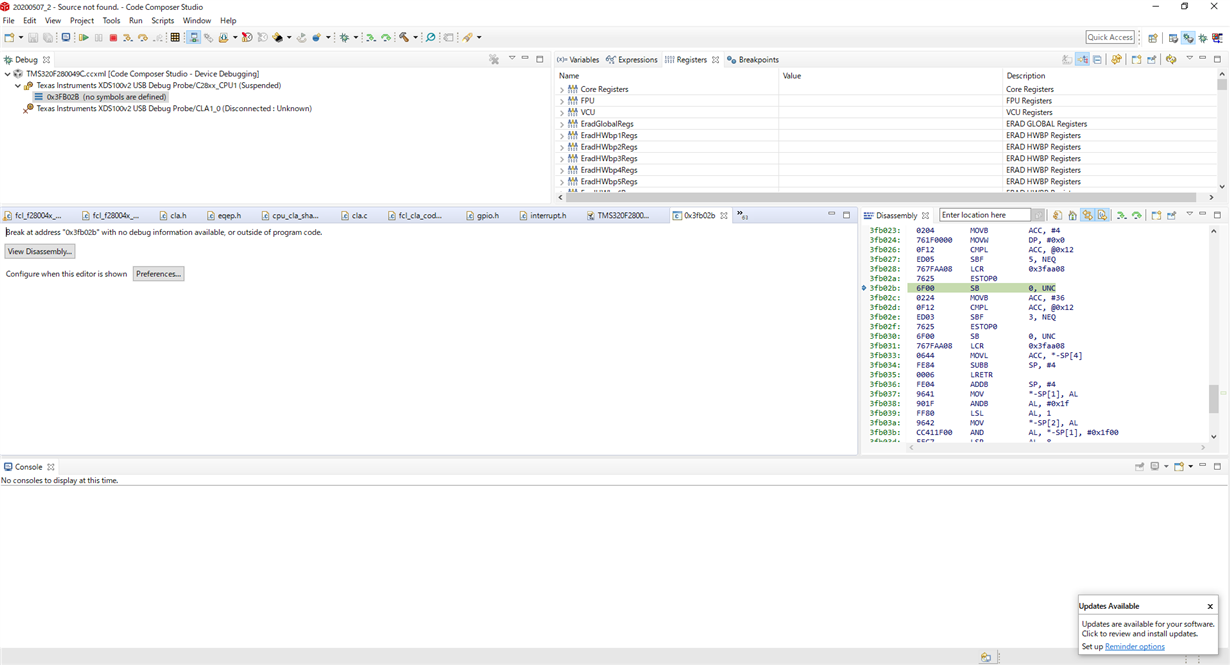

The failure condition with “iddk_servo_2837x_flash_lnk_cpu1.txt” is that the program does not work after powered on.

With CCS debug -> RUN works fine.

It seems that their .cmd causes the problem.

Could you please investigate the contents of the attached file?

Thank you in advance for your time check.

Best regards,

Hitoshi

//#############################################################################

//

// FILE: iddk_servo_2837x_flash_lnk_cpu1.cmd

//

//#############################################################################

// $TI Release: MotorControl SDK v2.01.00.00 $

// $Release Date: Mon Nov 11 15:18:12 CST 2019 $

// $Copyright:

// Copyright (C) 2017-2019 Texas Instruments Incorporated

//

// http://www.ti.com/ ALL RIGHTS RESERVED

// $

//#############################################################################

// In addition to this memory linker command file,

// add the header linker command file directly to the project.

// The header linker command file is required to link the

// peripheral structures to the proper locations within

// the memory map.

//

// For BIOS applications add: F28004x_Headers_BIOS.cmd

// For nonBIOS applications add: F28004x_Headers_nonBIOS.cmd

//

// The user must define CLA_C in the project linker settings if using the

// CLA C compiler

// Project Properties -> C2000 Linker -> Advanced Options -> Command File

// Preprocessing -> --define

#ifdef CLA_C

// Define a size for the CLA scratchpad area that will be used

// by the CLA compiler for local symbols and temps

// Also force references to the special symbols that mark the

// scratchpad are.

CLA_SCRATCHPAD_SIZE = 0x100;

--undef_sym=__cla_scratchpad_end

--undef_sym=__cla_scratchpad_start

#endif //CLA_C

MEMORY

{

/* BEGIN is used for the "boot to SARAM" bootloader mode */

RESET : origin = 0x3FFFC0, length = 0x000002

BEGIN : origin = 0x080000, length = 0x000002

/* FLASH_BANK0_SEC0 : origin = 0x080002, length = 0x000FFE*/ /* on-chip Flash */

/* FLASH_BANK0_SEC1 : origin = 0x081000, length = 0x001000*/ /* on-chip Flash */

/* FLASH_BANK0_SEC2 : origin = 0x082000, length = 0x001000*/ /* on-chip Flash */

/* FLASH_BANK0_SEC3 : origin = 0x083000, length = 0x001000*/ /* on-chip Flash */

/* FLASH_BANK0_SEC4 : origin = 0x084000, length = 0x001000*/ /* on-chip Flash */

/* FLASH_BANK0_SEC5 : origin = 0x085000, length = 0x001000*/ /* on-chip Flash */

/* FLASH_BANK0_SEC6 : origin = 0x086000, length = 0x001000*/ /* on-chip Flash */

/* FLASH_BANK0_SEC7 : origin = 0x087000, length = 0x001000*/ /* on-chip Flash */

// FLASH_BANK0_SEC8 : origin = 0x088000, length = 0x001000 /* on-chip Flash */

/* FLASH_BANK0_SEC9 : origin = 0x089000, length = 0x001000*/ /* on-chip Flash */

/* FLASH_BANK0_SEC10 : origin = 0x08A000, length = 0x001000*/ /* on-chip Flash */

FLASH_BANK0_SEC0_10 : origin = 0x080002, length = 0x00AFFE /* on-chip Flash */

/* FLASH_BANK0_SEC11 : origin = 0x08B000, length = 0x001000*/ /* on-chip Flash */

/* FLASH_BANK0_SEC12 : origin = 0x08C000, length = 0x001000*/ /* on-chip Flash */

/* FLASH_BANK0_SEC13 : origin = 0x08D000, length = 0x001000*/ /* on-chip Flash */

/* FLASH_BANK0_SEC14 : origin = 0x08E000, length = 0x001000*/ /* on-chip Flash */

FLASH_BANK0_SEC11_14 : origin = 0x08B000, length = 0x004000 /* on-chip Flash */

FLASH_BANK0_SEC15 : origin = 0x08F000, length = 0x001000 /* on-chip Flash */

/* BANK 1 */

FLASH_BANK1_SEC0 : origin = 0x090000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC1 : origin = 0x091000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC2 : origin = 0x092000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC3 : origin = 0x093000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC4 : origin = 0x094000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC5 : origin = 0x095000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC6 : origin = 0x096000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC7 : origin = 0x097000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC8 : origin = 0x098000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC9 : origin = 0x099000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC10 : origin = 0x09A000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC11 : origin = 0x09B000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC12 : origin = 0x09C000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC13 : origin = 0x09D000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC14 : origin = 0x09E000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC15 : origin = 0x09F000, length = 0x001000 /* on-chip Flash */

BOOTROM : origin = 0x3FF27C, length = 0x000D44

BOOT_RSVD : origin = 0x000002, length = 0x0000F3 /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x0000F5, length = 0x00030B

RAMM1 : origin = 0x000400, length = 0x000400 /* on-chip RAM block M1 */

CLA1_MSGRAMLOW : origin = 0x001480, length = 0x000080

CLA1_MSGRAMHIGH : origin = 0x001500, length = 0x000080

/* RAMLS0 : origin = 0x008000, length = 0x000800 */

/* RAMLS1 : origin = 0x008800, length = 0x000800 */

RAMLS0_1 : origin = 0x008000, length = 0x001000

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

RAMLS4 : origin = 0x00A000, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMLS6 : origin = 0x00B000, length = 0x000800

RAMLS7 : origin = 0x00B800, length = 0x000800

RAMGS0 : origin = 0x00C000, length = 0x002000

RAMGS1 : origin = 0x00E000, length = 0x002000

/* RAMGS2 : origin = 0x010000, length = 0x002000*/

/* RAMGS3 : origin = 0x012000, length = 0x002000*/

RAMGS2_3 : origin = 0x010000, length = 0x004000

}

SECTIONS

{

/* Setup for "boot to SARAM" mode:

The codestart section (found in DSP28_CodeStartBranch.asm)

re-directs execution to the start of user code. */

codestart : > BEGIN

// .text : >> FLASH_BANK0_SEC0 | FLASH_BANK0_SEC1 | FLASH_BANK0_SEC2

.text : >> FLASH_BANK0_SEC0_10, ALIGN(4) /* , ALIGN(4)*/

// .cinit : > FLASH_BANK0_SEC3

// .switch : > FLASH_BANK0_SEC3

.cinit : > FLASH_BANK0_SEC15, ALIGN(4) /* , ALIGN(4)*/

.switch : > FLASH_BANK0_SEC15

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMM1

#if defined(__TI_EABI__)

// .init_array : > FLASH_BANK0_SEC3, ALIGN(4)

.init_array : > FLASH_BANK0_SEC15, ALIGN(4)

// .bss : > RAMGS3

// .bss:output : > RAMGS3

// .bss:cio : > RAMGS3

// .data : > RAMGS3

// .sysmem : > RAMGS3

.bss : > RAMGS2_3, ALIGN(4) /* , ALIGN(4)*/

.bss:output : > RAMGS2_3, ALIGN(4) /* , ALIGN(4)*/

.bss:cio : > RAMGS2_3, ALIGN(4) /* , ALIGN(4)*/

.data : > RAMGS2_3, ALIGN(4) /* , ALIGN(4)*/

.sysmem : > RAMGS2_3, ALIGN(4) /* , ALIGN(4)*/

/* Initalized sections go in Flash */

// .const : > FLASH_BANK0_SEC3, ALIGN(4)

.const : > FLASH_BANK0_SEC11_14 , ALIGN(4)

#else

.pinit : > FLASH_BANK0_SEC15, PAGE = 0, ALIGN(4)

// .ebss : > RAMGS3, PAGE = 1

// .esysmem : > RAMGS3, PAGE = 1

// .cio : > RAMGS3, PAGE = 1

.ebss : > RAMGS2_3, PAGE = 1

.esysmem : > RAMGS2_3, PAGE = 1

.cio : > RAMGS2_3, PAGE = 1

.econst : > FLASH_BANK0_SEC15, PAGE = 0, ALIGN(4)

#endif

#if defined(__TI_EABI__)

.TI.ramfunc : {

--library = PM_tformat_lib_f28004x.lib (.text)

// } LOAD = FLASH_BANK0_SEC4,

} LOAD = FLASH_BANK1_SEC0,

RUN = RAMLS0_1,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(4)

#else

.TI.ramfunc : {

--library = PM_tformat_lib_f28004x.lib (.text)

// } LOAD = FLASH_BANK0_SEC4,

} LOAD = FLASH_BANK1_SEC0,

RUN = RAMLS0_1,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

PAGE = 0, ALIGN(4)

#endif

#if defined(__TI_EABI__)

/* CLA specific sections */

// Cla1Prog : LOAD = FLASH_BANK0_SEC4,

Cla1Prog : LOAD = FLASH_BANK1_SEC0,

RUN = RAMLS4 | RAMLS5,

LOAD_START(Cla1funcsLoadStart),

LOAD_END(Cla1funcsLoadEnd),

RUN_START(Cla1funcsRunStart),

LOAD_SIZE(Cla1funcsLoadSize),

ALIGN(4)

#else

/* CLA specific sections */

// Cla1Prog : LOAD = FLASH_BANK0_SEC4,

Cla1Prog : LOAD = FLASH_BANK1_SEC0,

RUN = RAMLS4 | RAMLS5,

LOAD_START(Cla1funcsLoadStart),

LOAD_END(Cla1funcsLoadEnd),

RUN_START(Cla1funcsRunStart),

LOAD_SIZE(Cla1funcsLoadSize),

PAGE = 0, AALIGN(4)

#endif

ClaData : > RAMLS3, ALIGN=2

Cla1ToCpuMsgRAM : > CLA1_MSGRAMLOW

CpuToCla1MsgRAM : > CLA1_MSGRAMHIGH

/* SFRA specific sections */

// SFRA_F32_Data : > RAMGS3, ALIGN = 64

SFRA_F32_Data : > RAMGS2_3, ALIGN = 64

#ifdef CLA_C

/* CLA C compiler sections */

//

// Must be allocated to memory the CLA has write access to

//

CLAscratch :

{ *.obj(CLAscratch)

. += CLA_SCRATCHPAD_SIZE;

*.obj(CLAscratch_end) } > RAMLS2, ALIGN=2

.scratchpad : > RAMLS2

.bss_cla : > RAMLS2

// .const_cla : LOAD = FLASH_BANK0_SEC3,

.const_cla : LOAD = FLASH_BANK0_SEC15,

RUN = RAMLS4 | RAMLS5,

RUN_START(Cla1ConstRunStart),

LOAD_START(Cla1ConstLoadStart),

LOAD_SIZE(Cla1ConstLoadSize),

ALIGN(2)

#endif //CLA_C

}

//===========================================================================

// End of file.

//===========================================================================