Hi

I have an issue of TMS32F280049C on a 6.6kw OBC project. The update of value in CMPA (EPWM1) is incorrect at line zero cross. CMPA is written by a value approximate 100%, but the duty of PWM from DSP output is approximate 0%. the error is often incidental.

Here are a party of source code and waveform:

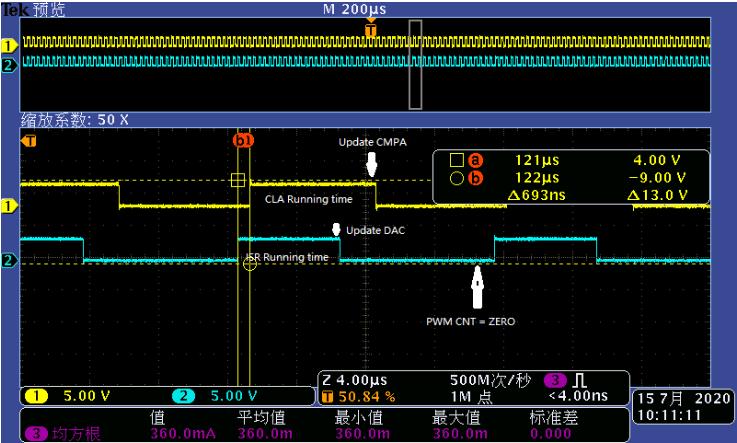

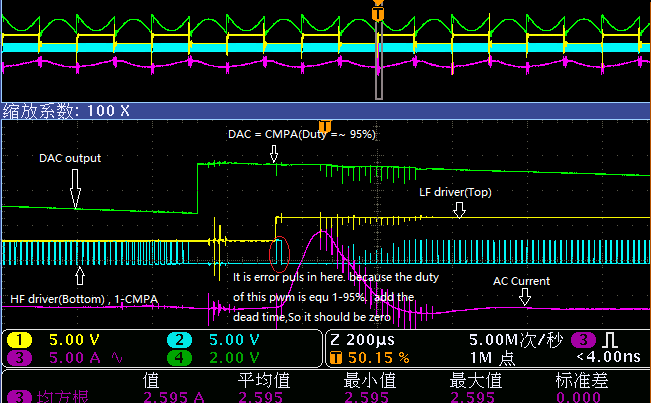

1:Waveform

The 4th Channel: DAC output according to variable "PFC_Duty" . It is correct in Red circle position.

The 1st Channel: PWM output according to variable "PFC_Duty" . It is incorrect in Red circle position.

The 2nd Channel: PWM complementary output with 1st channel . It is incorrect in Red circle position.

2. Source code

interrupt void ISR4(void) ----->is called every 14.92us

{

EINT;

Grid_Vols = (float)PFC_V_GRID_ADCREAD - 2505.0f;

Grid_Vols = Grid_Vols * .42228;//.39196; //.4259;//.3; // Scale to real world volts

CLA_forceTasks(CLA1_BASE,CLA_TASKFLAG_2); ----->To trigger task 2 in CLA

....

DAC_Output_Val = (DAC_Output[4]*0.0000152587890625)*5;

DAC_setShadowValue(DACA_BASE, DAC_Output_Val);

} ------>about 5us for this routine

static inline void CLA_TASK2(void)

{

....

cla_temp =(uint32_t)(PFC_Duty*65536.0);

DAC_Output[4]=cla_temp;

HWREG(PFC_LEG1_PWM_BASE + HRPWM_O_CMPA) = cla_temp;

cla_temp = (uint32_t)(PFCDB*65536.0);

HWREG(PFC_LEG1_PWM_BASE + HRPWM_O_DBREDHR) = cla_temp;

HWREG(PFC_LEG1_PWM_BASE + HRPWM_O_DBFEDHR) = cla_temp;

} ------>about 13us for this routine

Please help advise the possibilities. Thanks.