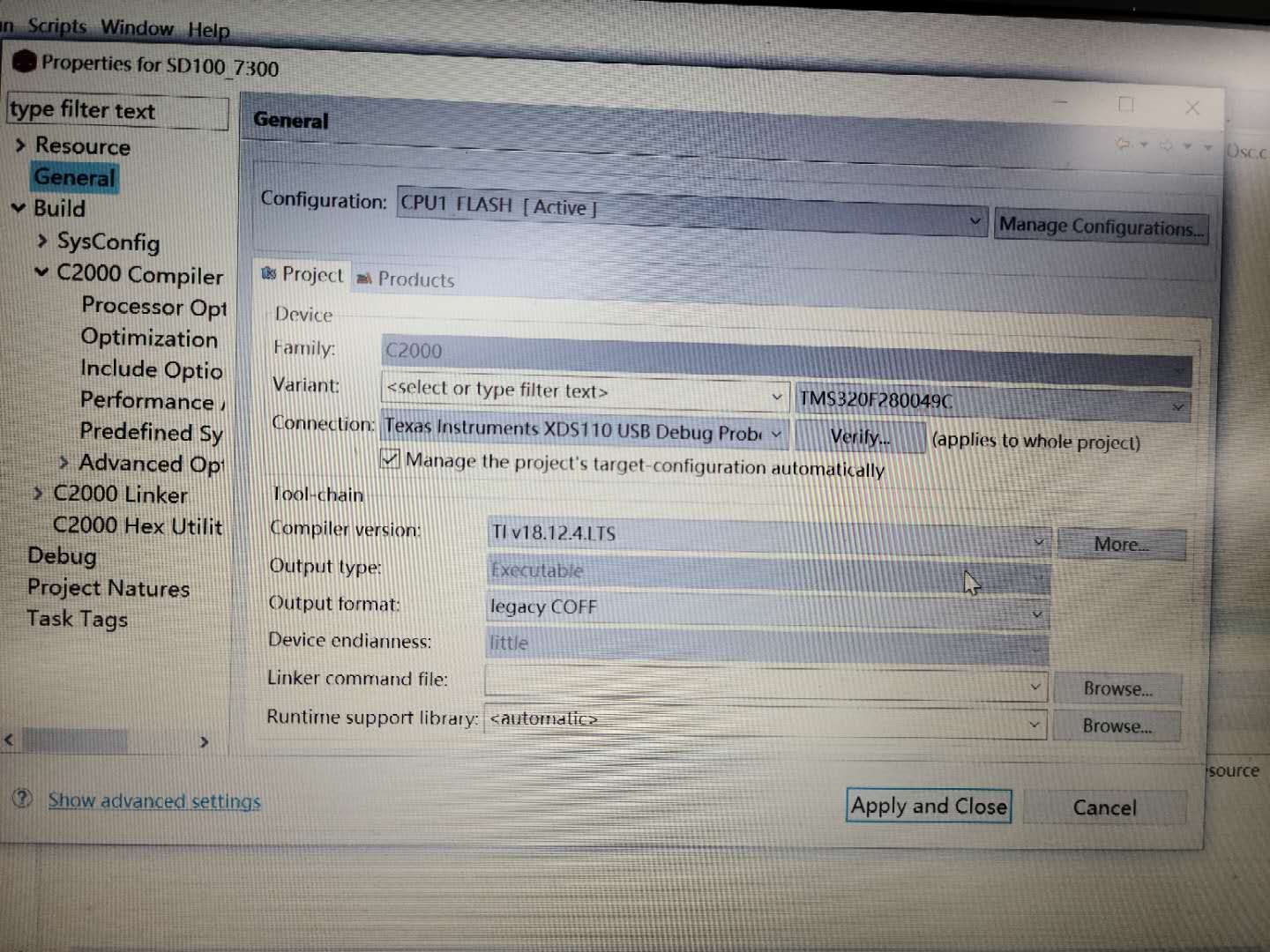

Tool/software: TI C/C++ Compiler

Hi Team,

My customer used F280049 CLA software resolver library Resolver_Lib_CLA_Float.lib, and reported an "#17003-D Warning", while removed the Resolver_Lib_CLA_Float.lib file, this warning removed; also has enlarger the size of CLA_scratchpad_SIZE and not removed the file, the warning still existed;

Description Resource Path Location Type

<a href="processors.wiki.ti.com/.../17003"> relocation to symbol "CLAscratch_end" overflowed; the 5-bit relocated address 0xf6 is too large to encode in the 16-bit unsigned field (type = 'R_ABS16_OC' (107), file = "../12_CLA/lib/Resolver_Lib_CLA_float.lib<Resolver_CLA_Source.obj>", offset = 0x00000326, section = "Cla1Prog") SD100_7300 C/C++ Problem

could you kindly give comments on how to remove the warning? Expect for your reply, thanks.

Best Regards

Benjamin