Other Parts Discussed in Thread: C2000WARE

HI everybody ,

in attached word you can see also code and scope screnshot , basically adc timing does not match what expecting :

ADC TIMING Issues details :

Condition

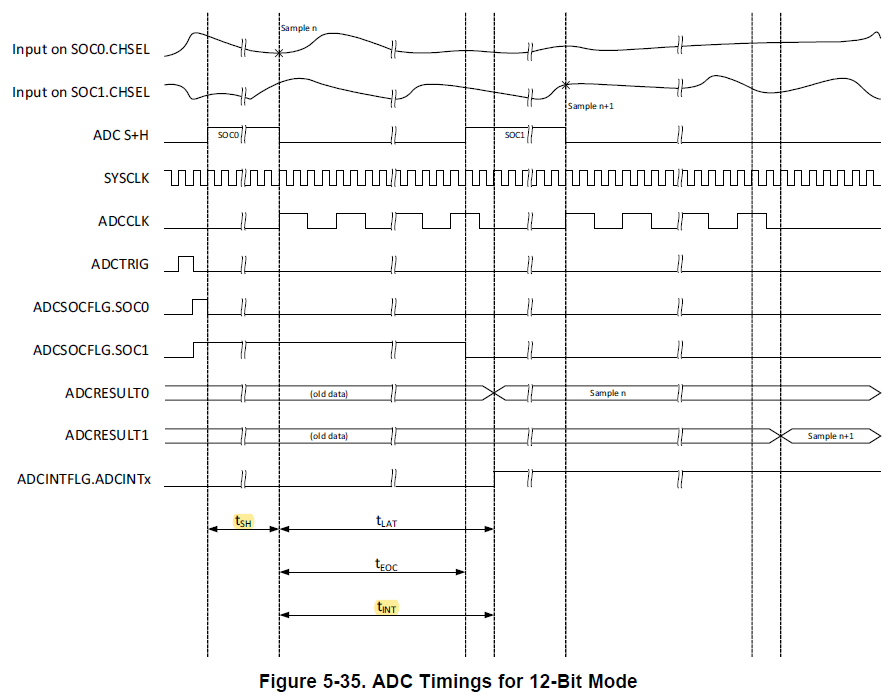

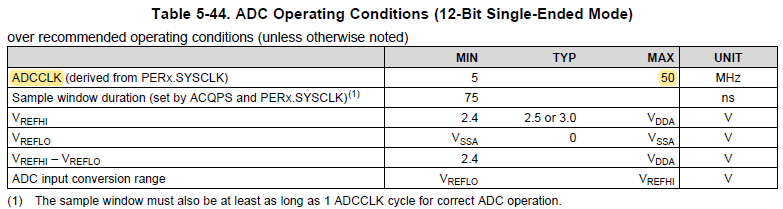

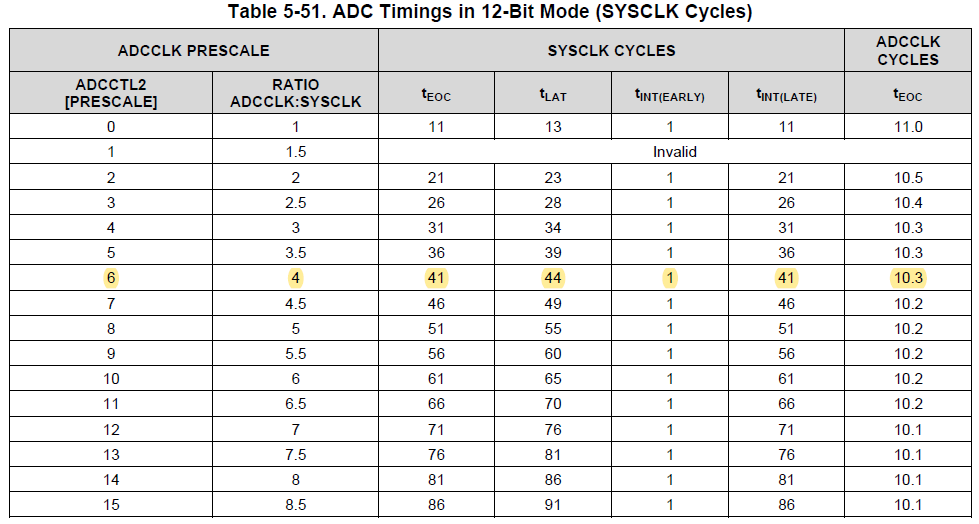

- SYSCLK is 200MHz, which is 5ns.

- ePWM triggers ADC SOC at 40kHz period.

Code in attached word

- Configured three ADC SOCs by using the same channel, ADCA CH_IN0.

- To test I enabled only SOC0 first. And then, I enabled the rest of two to compare. When I did it, I also updated ADC_setInterruptSource to ADC_SOC_NUMBER0 or ADC_SOC_NUMBER2.

Code in attached word

- Trigger ADC ISR at the end of SOC2

- Using ADC DMA

Test

- Trigger ADC ISR at the end of ADC SOC0

- Yellow: PWM SYNC pulse

- Blue: ADC ISR Start

- ADC Sampling time for SOC0 is 1us (S/H windows is set to 200, which will be 200 x 5ns = 1us)

- The time between PWM SYNC pulse rising edge to the ADC ISR start point is about 1.42us. I did not include GPIO set time latency, but it looks the additional 420ns is longer than the value stated in the datasheet.

Scope in attached word

- Trigger ADC ISR at the end of ADC SOC2

- Yellow: PWM SYNC pulse

- Blue: ADC ISR Start

- ADC Sampling time for SOC0 is 2.5us (please see the code above. S/H window is set to 500, which will be 500 x 5ns = 2.5us)

- The time between PWM SYNC pulse rising edge to the ADC ISR start point is about 6.34us. This does not give me consistent result. I was expecting 2.5us + latency.

thank you

best regards

CarloADC TIMING Issues details.docx