Dear Veena,

We have faced same issue again with CLA1.

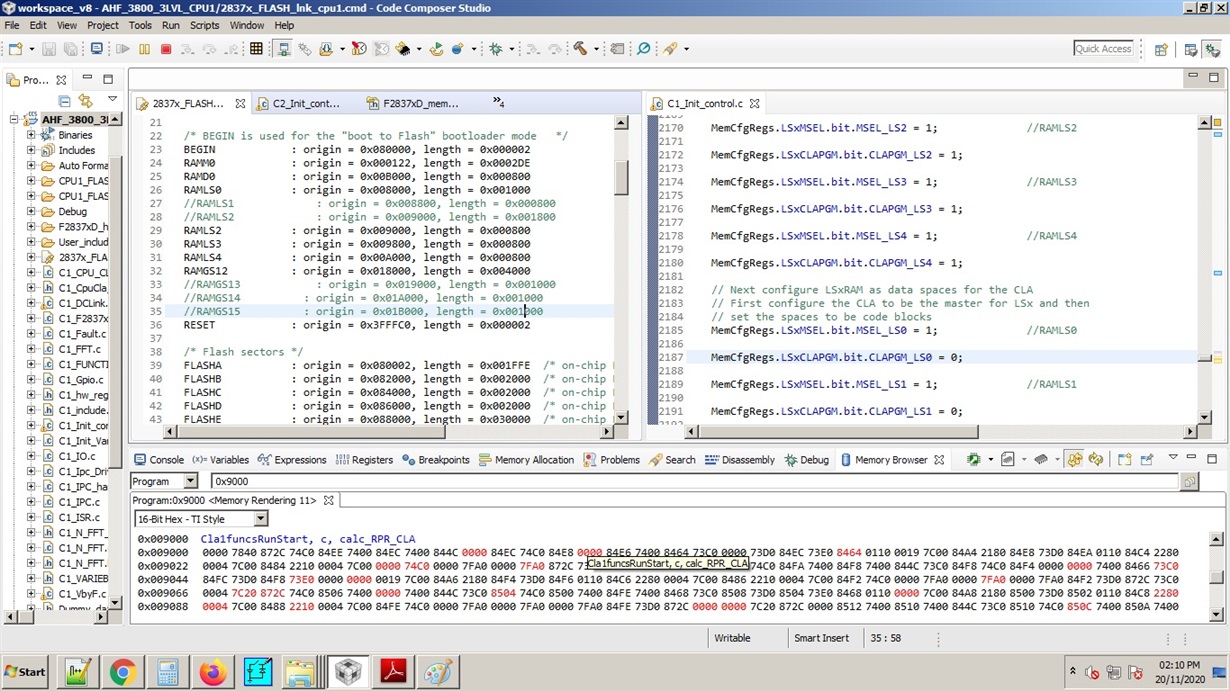

The function we have developed is not working properly. The function contains several equations, in which some part of function is working Ok but other part of function is not working.

I have attached two file here. One file is function written in C and other file is part of disassembly part of CCS debugger.

Kindly take serious Note of this problem.

Regards,

Dushyant RanaSource_File.rar