Dear TI engineer,

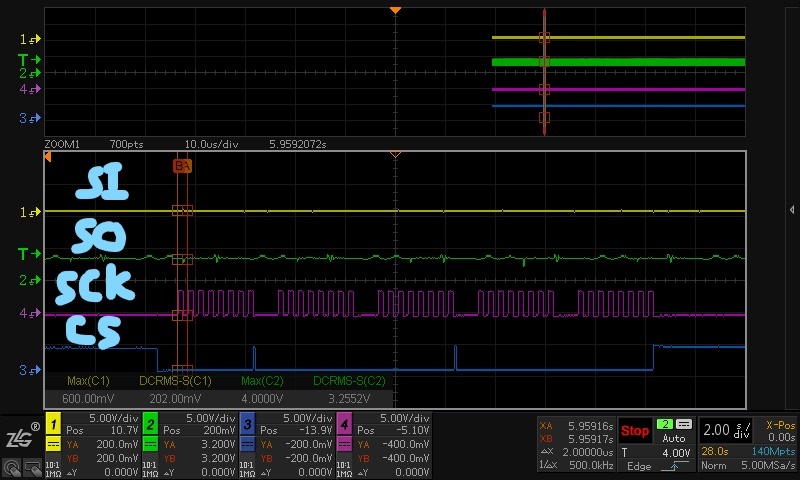

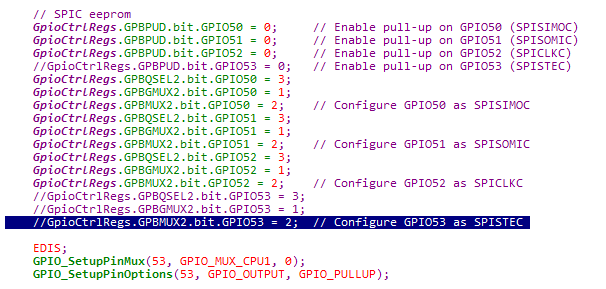

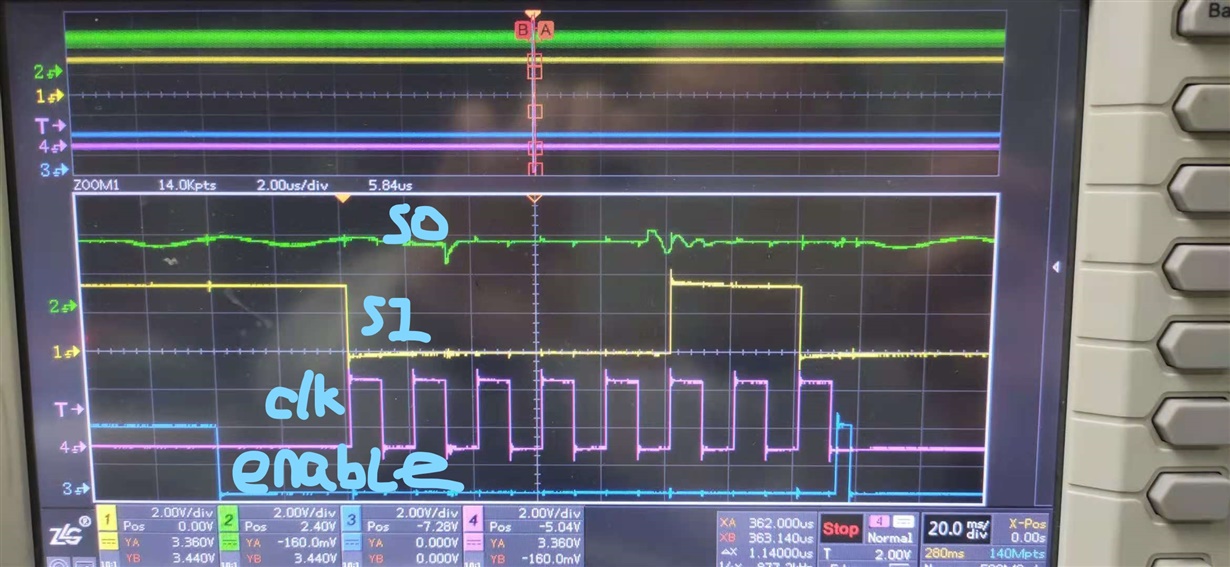

I would like to use spi to control eeprom named CAT25256. I config it according to reference. But it could not send data successfully. Though the clk seems no problem. The problem happened in sEE25256Init.

Could you help me? Looking forward for your reply.

//step1.

SpicRegs.SPICCR.bit.SPISWRESET = 0; //reset state,clear spi flag

//step2.

SpicRegs.SPICTL.bit.MASTER_SLAVE = 1; //master

SpicRegs.SPICCR.bit.SPILBK = 0;

SpicRegs.SPICCR.bit.CLKPOLARITY = 0; // output on rising edge, input on falling edge

SpicRegs.SPICTL.bit.CLK_PHASE = 0;

SpicRegs.SPIBRR.bit.SPI_BIT_RATE = 99; // 200M /4(default) /100 = 500 K

SpicRegs.SPICCR.bit.HS_MODE = 0; //disable high speed mode

SpicRegs.SPICCR.bit.SPICHAR = 0x07; // shift 8 bits as a charactor,fit eeprom

SpicRegs.SPIPRI.bit.TRIWIRE = 0; //4 wire mode

SpicRegs.SPIFFTX.bit.SPIFFENA = 1; // enable SPI FIFO enhance

SpicRegs.SPIFFTX.bit.TXFFINTCLR = 1; // clear TXFFINT flag

SpicRegs.SPIFFRX.bit.RXFFINTCLR = 1; // clear Receive FIFO Interrupt flag

SpicRegs.SPIFFRX.bit.RXFFOVFCLR = 1; //clear overflow flag

SpicRegs.SPIFFTX.bit.TXFIFO = 1; // Release transmit and receive FIFO resets

SpicRegs.SPIFFRX.bit.RXFIFORESET = 1;

SpicRegs.SPIFFTX.bit.SPIRST = 1;

//step3.

SpicRegs.SPICTL.bit.OVERRUNINTENA = 0; // disable receiver overrun interrupt

SpicRegs.SPICTL.bit.SPIINTENA = 0; // disable SPI interrupt

SpicRegs.SPIFFTX.bit.TXFFIL = 0; //TX FIFO interrupt generated when 16 words or fewer remaining in the TX buffer.

SpicRegs.SPIFFRX.bit.RXFFIL = 0;

SpicRegs.SPIFFTX.bit.TXFFIENA = 0; // disable FIFO tx INT

SpicRegs.SPIFFRX.bit.RXFFIENA = 0; // disable rx FIFO int

//step4.

SpicRegs.SPICTL.bit.TALK=1; // enable transmission

SpicRegs.SPIFFCT.all=0; // no delay between characters

SpicRegs.SPICCR.bit.SPISWRESET = 1;

/****************************************************************/