Hi expert,

this is the issue of SCI receive. the host which sent data is another MCU, and also checked with PC. The issue is always.

After we initialize the configuration of SCIA after power-on, we will encounter that sometimes the data cannot be received normally. At this time, the data can be received normally after initializing the configuration again. This phenomenon does not occur on every board. Some boards sometimes appear, which is quite confusing.

We check the SciaRegs.SCIFFRX.bit.RXFFST flag at a time of 200us to determine whether there is data to be received.

After the DSP is powered on, the SciaRegs.SCIFFRX.bit.RXFFST is checked in a 200us cycle, sometimes the "if( SciaRegs.SCIFFRX.bit.RXFFST != 0 )" cannot be checked.

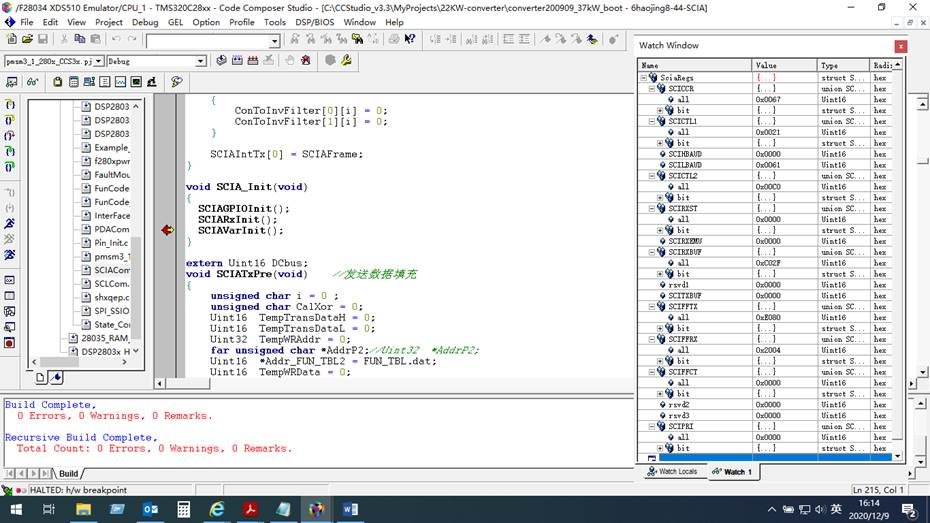

here I attached the initialized code.

以下是初始化程序(初始化为接收):

initial to receiver

void SCIAGPIOInit(void)

{

EALLOW;

//GpioCtrlRegs.GPAMUX1.bit.GPIO6 = 1; //use as Epwm4A ----ZCLK

//GpioCtrlRegs.GPAMUX2.bit.GPIO31 = 0; //use as output ----ZCRRSET

//GpioCtrlRegs.GPADIR.bit.GPIO31 = 1;

//GpioCtrlRegs.GPBMUX1.bit.GPIO34 = 0; //use as output ----ZTXEN

//GpioCtrlRegs.GPBDIR.bit.GPIO34 = 1;

GpioCtrlRegs.GPAPUD.bit.GPIO28 = 0; // Enable pull-up for GPIO28 (SCIRXDA)

GpioCtrlRegs.GPAPUD.bit.GPIO29 = 0; // Enable pull-up for GPIO29 (SCITXDA)

GpioCtrlRegs.GPAMUX2.bit.GPIO28 = 1; // Configure GPIO28 for SCIRXDA operation

GpioCtrlRegs.GPAMUX2.bit.GPIO29 = 1; // Configure GPIO29 for SCITXDA operation

/*

PieVectTable.SCIRXINTA = &SCIARxErrDeal;

PieCtrlRegs.PIEIER9.bit.INTx1=1; // PIE Group 9, INT1

IER |= 0x100; // Enable CPU INT

*/

EDIS;

}

void SCIARxInit(void)

{

EALLOW;

// Note: Clocks were turned on to the SCI peripheral in the InitSysCtrl() function

SciaRegs.SCICTL1.bit.SWRESET = 0;

SciaRegs.SCIFFTX.all=0xE040;

SciaRegs.SCIFFRX.all=0x2044;

SciaRegs.SCIFFCT.all=0x0;

SciaRegs.SCICCR.all =0x0067; // 1 stop bit, No loopback

// Even parity,8 char bits,

// async mode, idle-line protocol

//SciaRegs.SCICTL1.all =0x0001;//0x0041;//0x0043; //Enable RX ERR

//SciaRegs.SCICTL1.all =0x0003; // enable TX, RX, internal SCICLK,

// Disable RX ERR, SLEEP, TXWAKE

//SciaRegs.SCICTL2.all =0x0003;

//SciaRegs.SCICTL2.bit.TXINTENA =0;

//SciaRegs.SCICTL2.bit.RXBKINTENA =1;

//SciaRegs.SCIHBAUD =0x0000; // LSPCLK = 15MHz.

//SciaRegs.SCILBAUD =0x00C2; // 9600 bps

//SciaRegs.SCILBAUD =0x0061; // 19200 bps

//SciaRegs.SCILBAUD =0x0030; // 38400 bps

switch(SCIABaudSet)

{

case 0:

SciaRegs.SCIHBAUD =0x0000; // LSPCLK = 15MHz.

SciaRegs.SCILBAUD =0x00C2; // 9600 bps

break;

case 1:

SciaRegs.SCIHBAUD =0x0000; // LSPCLK = 15MHz.

SciaRegs.SCILBAUD =0x0061; // 19200 bps

break;

case 2:

SciaRegs.SCIHBAUD =0x0000; // LSPCLK = 15MHz.

SciaRegs.SCILBAUD =0x0030; // 38400 bps

break;

default:break;

}

//SciaRegs.SCIHBAUD =0x0000; // LSPCLK = 15MHz.

//SciaRegs.SCILBAUD =0x0060; // 19200 bps

//SciaRegs.SCIHBAUD =0x0000; // LSPCLK = 15MHz.

//SciaRegs.SCILBAUD =0x000E; // 125K bps

SciaRegs.SCICTL1.bit.RXENA = 1;

SciaRegs.SCICTL1.bit.TXENA = 0;

SciaRegs.SCICTL1.bit.SWRESET = 1;

//SciaRegs.SCICTL1.all =0x0023; // Relinquish SCI from Reset

EDIS;

}

void SCIATxInit(void)

{

EALLOW;

// Note: Clocks were turned on to the SCI peripheral in the InitSysCtrl() function

SciaRegs.SCICTL1.bit.SWRESET = 0;

SciaRegs.SCIFFTX.all=0xE040;

SciaRegs.SCIFFRX.all=0x2044;

SciaRegs.SCIFFCT.all=0x0;

SciaRegs.SCICCR.all =0x0067; // 1 stop bit, No loopback

// Even parity,8 char bits,

// async mode, idle-line protocol

//SciaRegs.SCICTL1.all =0x0002; //enable Tx cls Rx

//SciaRegs.SCICTL1.all =0x0003; // enable TX, RX, internal SCICLK,

// Disable RX ERR, SLEEP, TXWAKE

//SciaRegs.SCICTL2.all =0x0002;

//SciaRegs.SCICTL2.bit.TXINTENA =1;

//SciaRegs.SCICTL2.bit.RXBKINTENA =0;

//SciaRegs.SCIHBAUD =0x0000; // LSPCLK = 15MHz.

//SciaRegs.SCILBAUD =0x00C2; // 9600 bps

//SciaRegs.SCILBAUD =0x0061; // 19200 bps

//SciaRegs.SCILBAUD =0x0030; // 38400 bps

switch(SCIABaudSet)

{

case 0:

SciaRegs.SCIHBAUD =0x0000; // LSPCLK = 15MHz.

SciaRegs.SCILBAUD =0x00C2; // 9600 bps

break;

case 1:

SciaRegs.SCIHBAUD =0x0000; // LSPCLK = 15MHz.

SciaRegs.SCILBAUD =0x0061; // 19200 bps

break;

case 2:

SciaRegs.SCIHBAUD =0x0000; // LSPCLK = 15MHz.

SciaRegs.SCILBAUD =0x0030; // 38400 bps

break;

default:break;

}

//SciaRegs.SCIHBAUD =0x0000; // LSPCLK = 15MHz.

//SciaRegs.SCILBAUD =0x0060; // 19200 bps

//SciaRegs.SCIHBAUD =0x0000; // LSPCLK = 15MHz.

//SciaRegs.SCILBAUD =0x000E; // 125K bps

SciaRegs.SCICTL1.bit.RXENA = 0;

SciaRegs.SCICTL1.bit.TXENA = 1;

SciaRegs.SCICTL1.bit.SWRESET = 1;

//SciaRegs.SCICTL1.all =0x0023; // Relinquish SCI from Reset

EDIS;

}

void SCIAVarInit(void)

{

unsigned int i = 0;

SCIAIntRxCnt = 0;

SCIAIntTxCnt = 0;

SCIAIntTxLen = 0;

SCIAIdleCnt = 0;

SCIAStatus = 0;

SCIAKey = 0;

SCIATxTimeCnt = 0;

for( i = 0; i< SCIARXMAX ; i++ )

{

SCIARxApp.SCIARxAppArray[i] = 0;

SCIAIntRx[i] = 0;

}

for( i = 0; i< SCIATXMAX ; i++ )

{

SCIATxApp.SCIATxAppArray[i] = 0;

SCIAIntTx[i] = i;//0;

}

for( i = 0; i< SCIAFILTERTIME ; i++)

{

ConToInvFilter[0][i] = 0;

ConToInvFilter[1][i] = 0;

}

SCIAIntTx[0] = SCIAFrame;

}

void SCIA_Init(void)

{

SCIAGPIOInit();

SCIARxInit();

SCIAVarInit();

}

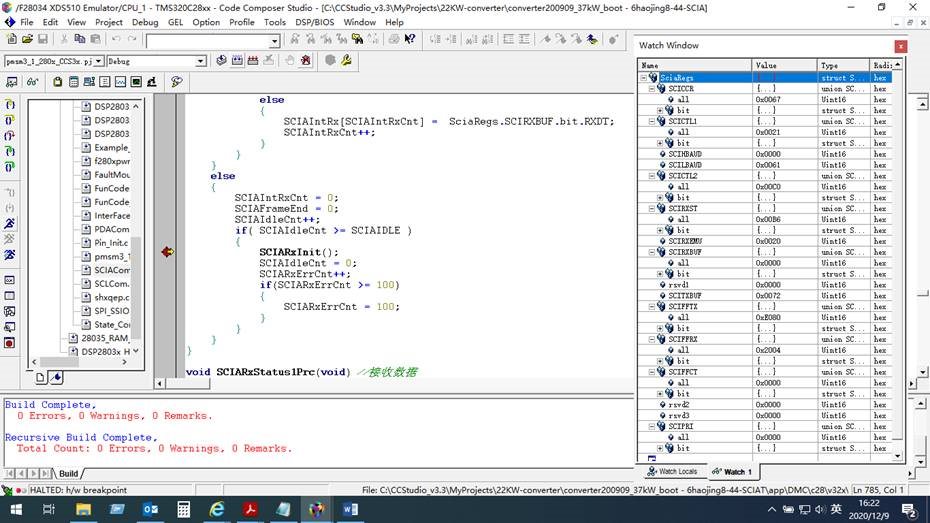

以下是判断是否有接收数据:

to judge whether there is data

void SCIARxStatus0Prc(void)

{

if( SciaRegs.SCIFFRX.bit.RXFFST != 0 )

{ //有接收到数据,进入接收状态

SCIAStatus = 1;

SCIAFrameEnd = 0;

SCIAIdleCnt = 0;

while(SciaRegs.SCIFFRX.bit.RXFFST != 0 )

{

if(SCIAIntRxCnt >= SCIARXMAX)

{ //防止接收异常,异常处理后下一帧正常

SCIAIntRxCnt = 0;

SCIAStatus = 0;

return;

}

else

{

SCIAIntRx[SCIAIntRxCnt] = SciaRegs.SCIRXBUF.bit.RXDT;

SCIAIntRxCnt++;

}

}

}

else

{

SCIAIntRxCnt = 0;

SCIAFrameEnd = 0;

SCIAIdleCnt++;

if( SCIAIdleCnt >= SCIAIDLE )

{

SCIAIdleCnt = 0;

SCIARxErrCnt++;

if(SCIARxErrCnt >= 100)

{

SCIARxErrCnt = 100;

}

}

}

}

below is the normal condition register status

for abnormal status, the SCIRXST is changed to 0x00B6 or 0x00B2.

Could you kindly review it and give some comments?

BR

Emma