Hi,

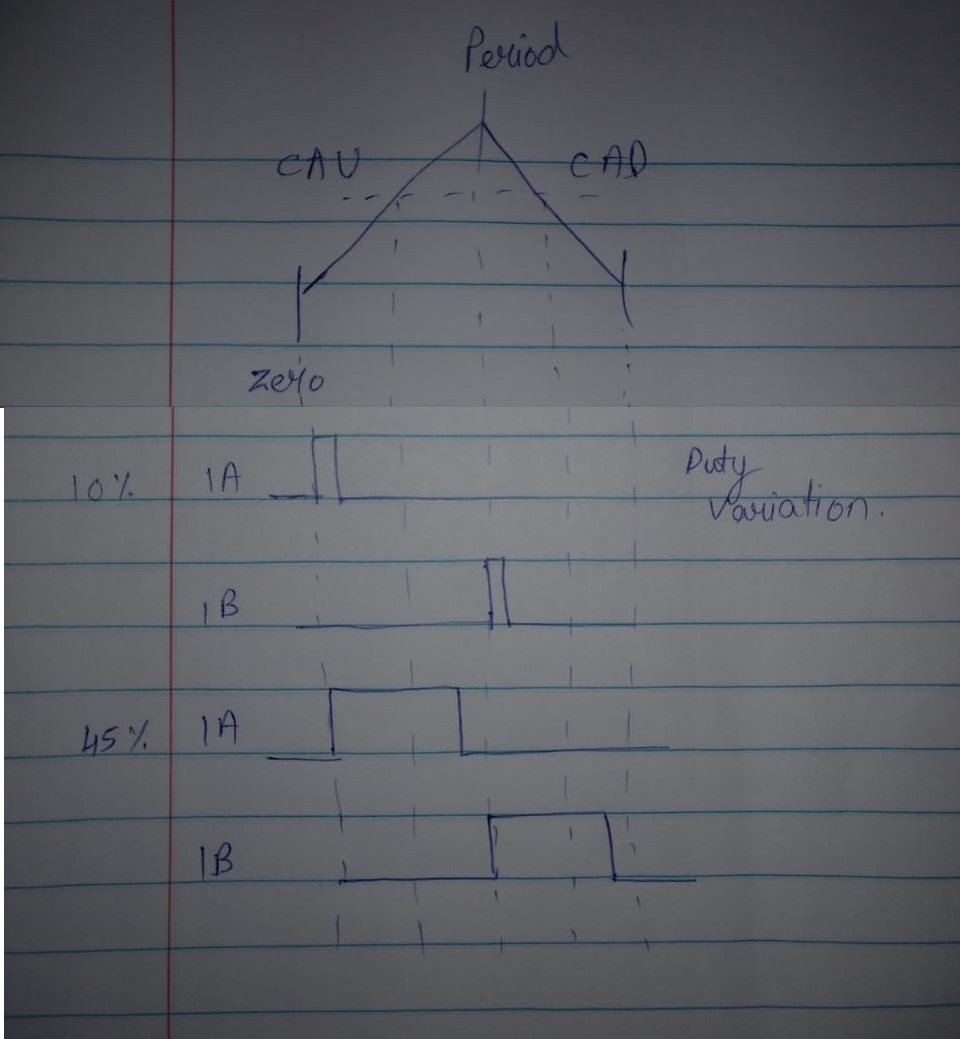

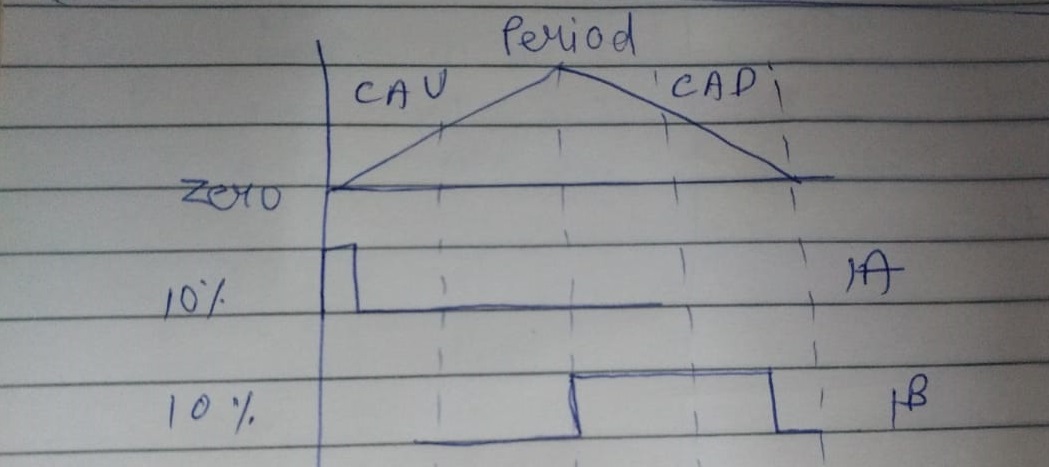

I wanted to generate 2 pulses from ePWM 1A and 1B. 1A sets at zero and clears at CAU, 1B sets at PRD and clears at CAD. Im unable to get required. Please let me know if its possible.

currently used config:

EPwm1Regs.TBPRD = 3000; // 15kHz

EPwm1Regs.TBPHS.half.TBPHS = 0x0000;

EPwm1Regs.TBCTR = 0x0000;

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE;

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm1Regs.CMPA.half.CMPA = 2000; // can be varied

EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET;

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.PRD = AQ_SET;

EPwm1Regs.AQCTLB.bit.CBD = AQ_CLEAR;