Hi,

I am evaluating F280049C Launch pad for one of my applications. Everything was working fine until I added few lines of code and it is throwing link error as follows.

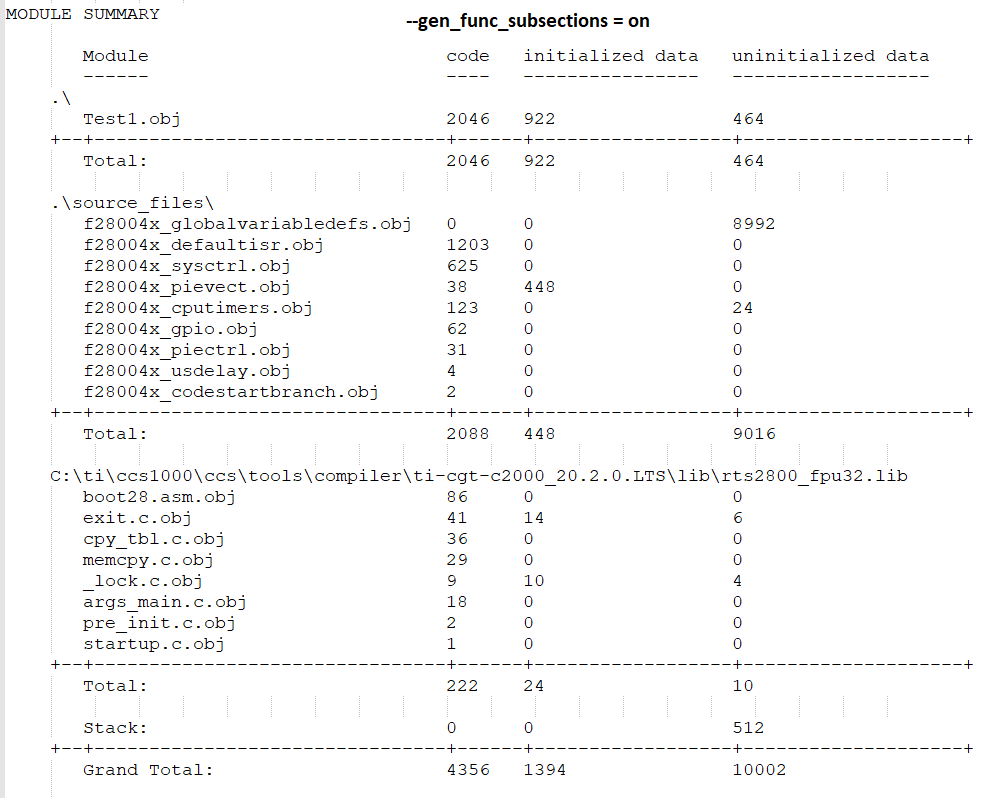

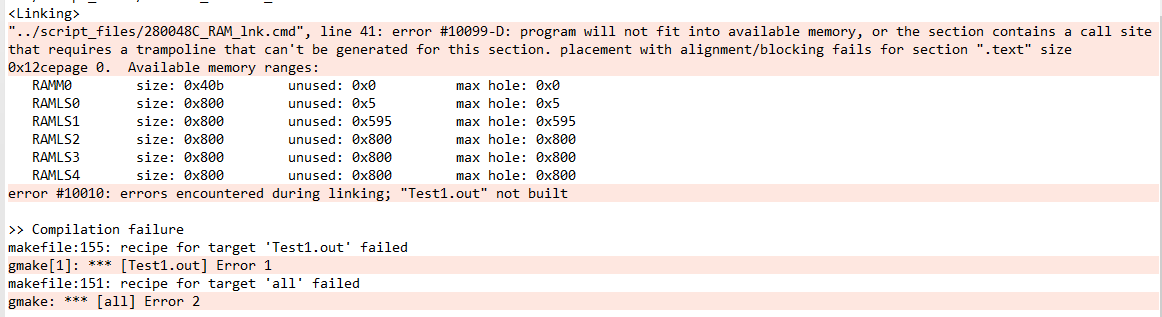

<Linking>

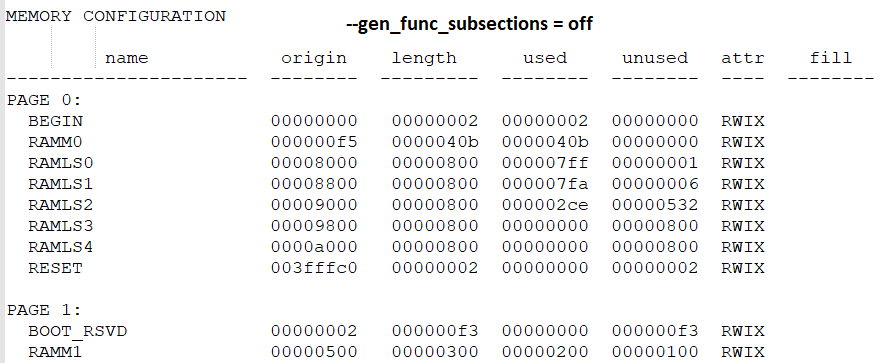

"../script_files/280048C_RAM_lnk.cmd", line 41: error #10099-D: program will not fit into available memory, or the section contains a call site that requires a trampoline that can't be generated for this section. placement with alignment/blocking fails for section ".text" size 0x136cpage 0. Available memory ranges:

RAMM0 size: 0x40b unused: 0x1 max hole: 0x1

RAMLS0 size: 0x800 unused: 0x6 max hole: 0x6

RAMLS1 size: 0x800 unused: 0x518 max hole: 0x518

RAMLS2 size: 0x800 unused: 0x800 max hole: 0x800

RAMLS3 size: 0x800 unused: 0x800 max hole: 0x800

RAMLS4 size: 0x800 unused: 0x800 max hole: 0x800

error #10010: errors encountered during linking; "Test1.out" not built

>> Compilation failure

makefile:155: recipe for target 'Test1.out' failed

gmake[1]: *** [Test1.out] Error 1

makefile:151: recipe for target 'all' failed

gmake: *** [all] Error 2

/* BEGIN is used for the "boot to SARAM" bootloader mode */

BEGIN : origin = 0x000000, length = 0x000002

RAMM0 : origin = 0x0000F5, length = 0x00040B

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

RAMLS4 : origin = 0x00A000, length = 0x000800

RESET : origin = 0x3FFFC0, length = 0x000002

PAGE 1 :

BOOT_RSVD : origin = 0x000002, length = 0x0000F3 /* Part of M0, BOOT rom will use this for stack */

RAMM1 : origin = 0x000500, length = 0x000300 /* on-chip RAM block M1 */

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMLS6 : origin = 0x00B000, length = 0x000800

RAMLS7 : origin = 0x00B800, length = 0x000800

RAMGS0 : origin = 0x00C000, length = 0x002000

RAMGS1 : origin = 0x00E000, length = 0x002000

RAMGS2 : origin = 0x010000, length = 0x002000

RAMGS3 : origin = 0x012000, length = 0x002000

}

SECTIONS

{

codestart : > BEGIN, PAGE = 0

.TI.ramfunc : > RAMM0 PAGE = 0

.text : >>RAMM0 | RAMLS0 | RAMLS1 | RAMLS2 | RAMLS3 | RAMLS4, PAGE = 0

.cinit : > RAMM0, PAGE = 0

.pinit : > RAMM0, PAGE = 0

.switch : > RAMM0, PAGE = 0

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used, */

.stack : > RAMM1, PAGE = 1

.ebss : > RAMLS5, PAGE = 1

.econst : > RAMLS5, PAGE = 1

.esysmem : > RAMLS5, PAGE = 1

ramgs0 : > RAMGS0, PAGE = 1

ramgs1 : > RAMGS1, PAGE = 1

}