Dear Team:

I have used F28335 and 28377S, and now I want to replace them with F28M35 as my main CPU.I have the following questions to consult, hoping to get a prompt reply. With regard to EPI functions, I have the following questions:

1, In the general purpose mode of EPI, the generation and termination of the Frame signal is not covered. I want to know the information about this.Is the signal valid at high level?

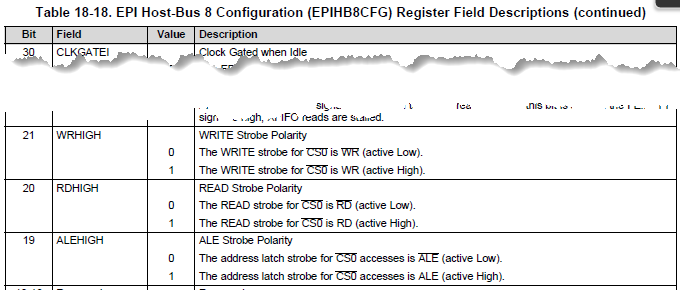

2, I want to extend a simple 8 bit wide parallel port to CPLD interface with the EPI function. However, I do not need too many address bits. At present, the 3 bit address is enough.What I want to know is whether the extra pins in the EPI function can be configured for other uses, such as GPIO, SCI, and so on.Have they been forced to occupy the EPI function tegether?

3, In the latest English datasheet of F28M35, figures 5-29 and 5-30 are confusing. Are the RD and WR pins in the EPI function valid at low level?Please note that I am asking the output of the pin itself. Because in this datesheet, when expressing RD and WR, sometimes it takes superscript, sometimes without superscript.

There are many problems. I am not sure whether I can express my doubts clearly. I look forward to your reply. Thanks very much.

Best Regards