Greeting,

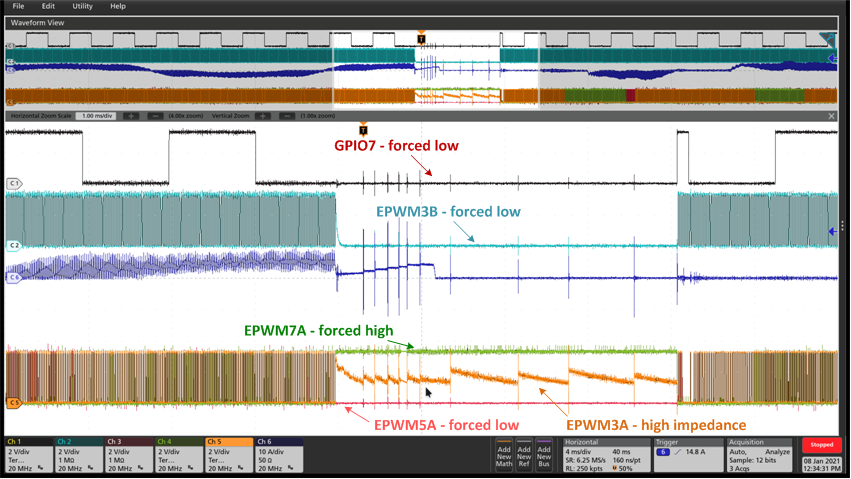

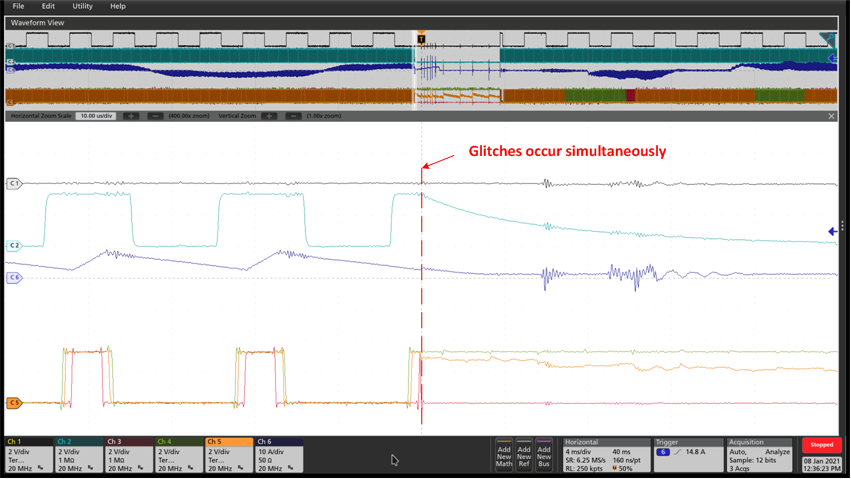

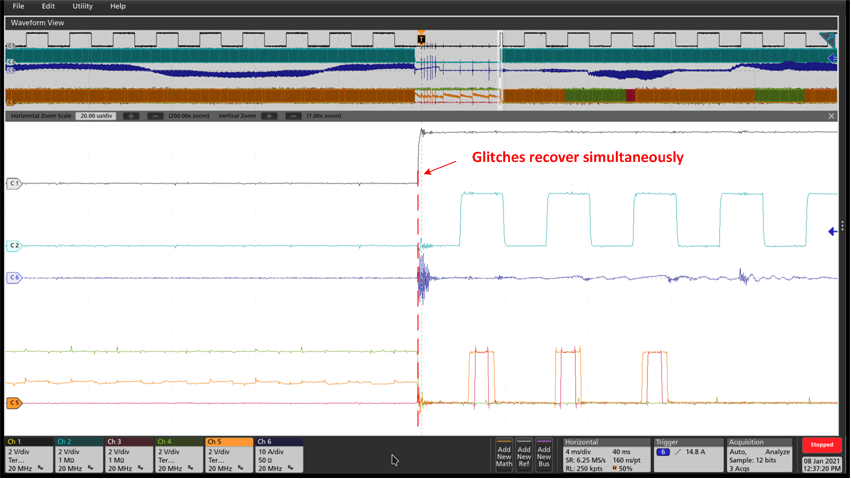

I am using F280049 for three phase PFC control, the problem occurred occasionally that EPWM and GPIO outputs is forced high, low, or high impedance. As shown the following scopes, Ch1 is the clock that I use Timer1 of 1ms to toggle GPIO7, Ch2 is a debug EPWM output does not connect the driver circuit and set 50% duty, Ch3-Ch5 are EPWM outputs to connect the driver circuit, Ch6 is a phase current for triggering scope.

I found all GPIO and EPWM glitches appear and recover simultaneously. Besides, CPU and analog modules are running because duty cycles of EPWM outputs are correct after recovery.

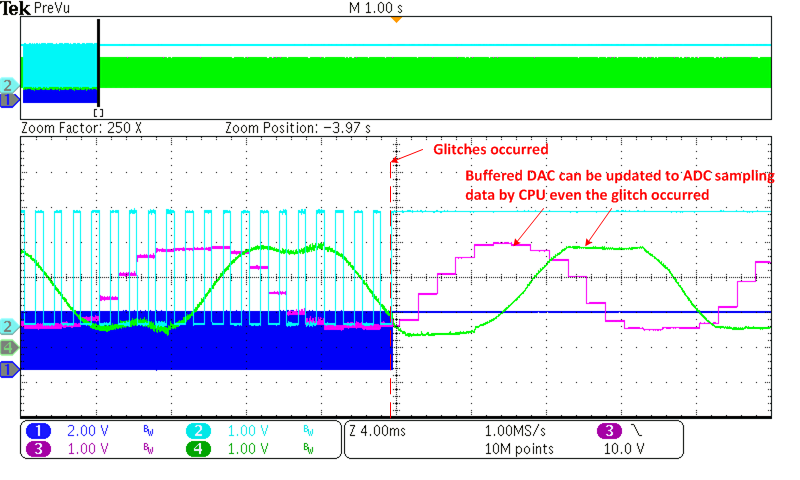

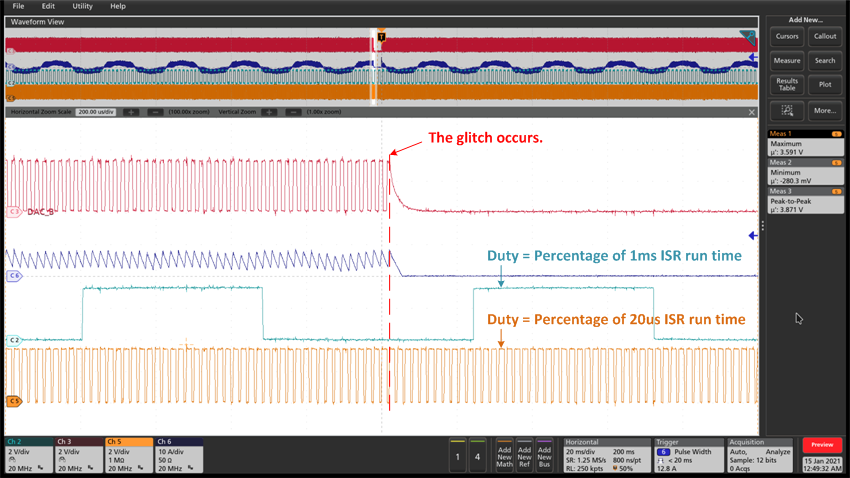

I also capture another scope shows DAC and ADC are running normally when the glitch occurred as below. Ch1 is a debug GPIO output triggered by 20us ISR run time, Ch2 is another debug GPIO output triggered by 1ms ISR run time, Ch3 is buffered DACA to output the ADC sampling of one phase voltage and updated in 1ms ISR, Ch4 is buffered DACB to output ADC sampling of another phase voltage and updated in 20us ISR. The scope shows ADC, DAC, and CPU are work normally when GPIO glitch occurred.

What will cause the digital peripheral module glitch like this? Any suggestions to avoid this issue?

Regards,

Watch