Dear Champs,

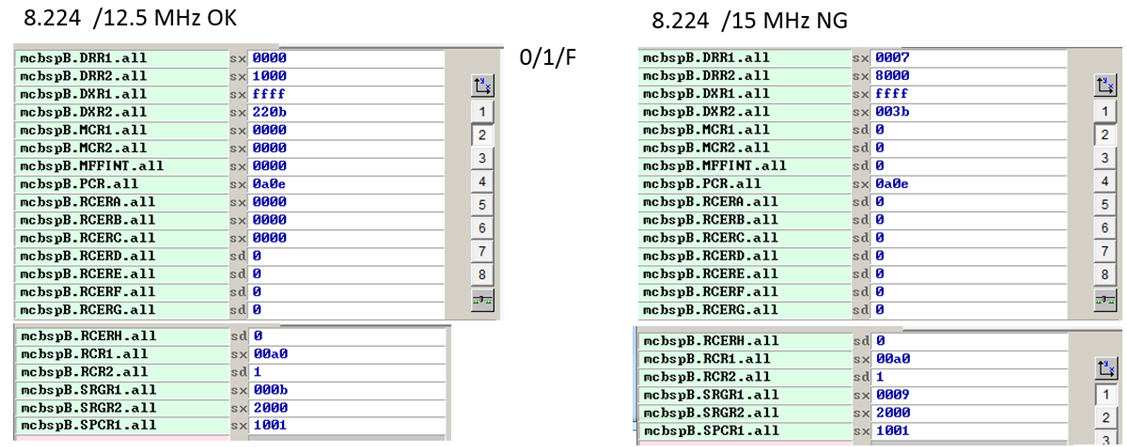

We used McBSP as SPI operation by using clock stop mode on F28335. According the register values we set, mcbspB.SPCR1.all= 0x1001h, it means bit12-11 is 10 for clock stop mode without clock delay. It means the clock starts immediately (CLKSTP = 10b) at the beginning of each data transfer.

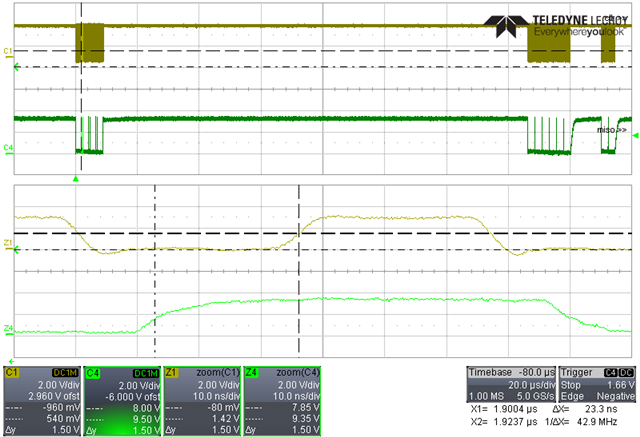

But we found it still need to add 2bit data delay on RCR2 for correct communication when CLKR is 15MHz.

There is a confusion for RDATDLY, “A data delay value of 0 or 2 is undefined in the clock stop mode”.

Does anyone know what is this contradiction?

If you have any suggestions, please feel free to let me know.

Thanks a lot.

Best regards,

Janet