Hi All,

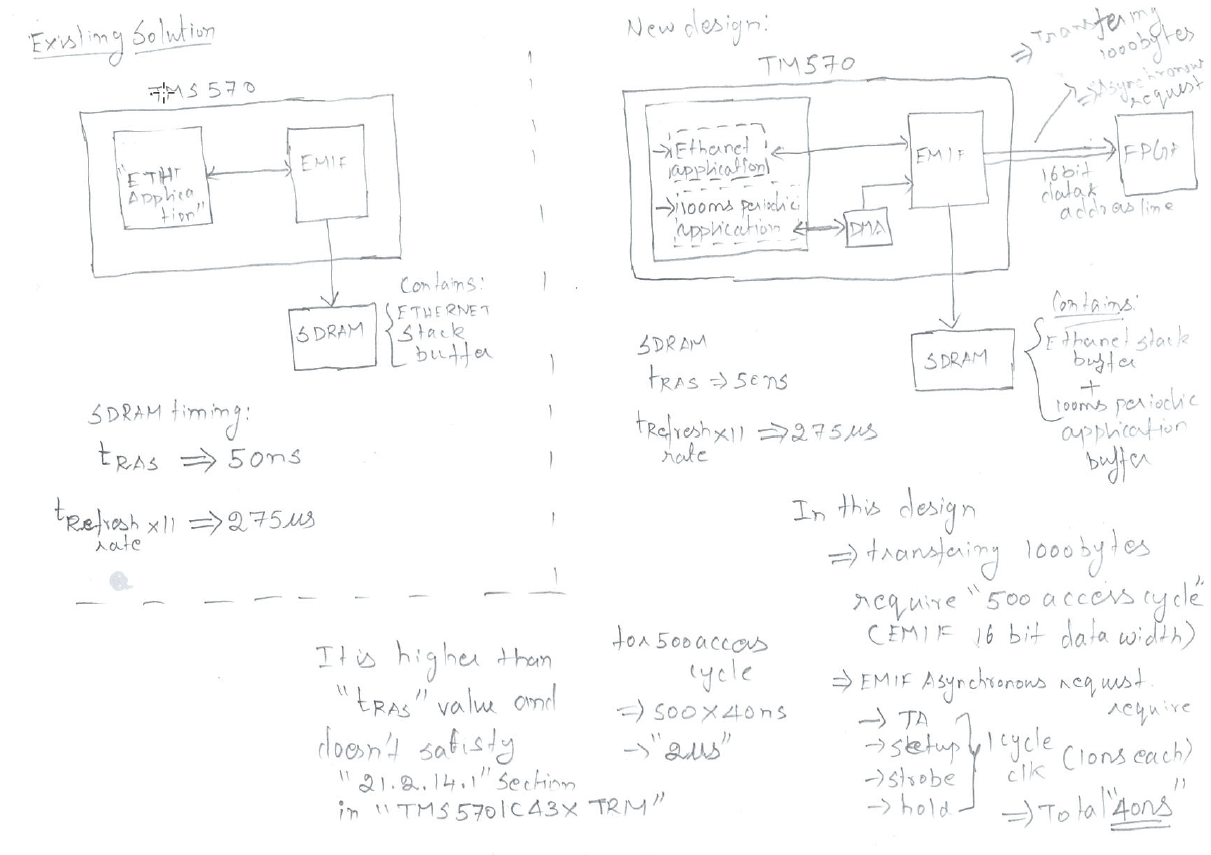

Existing Solution:

1) Ethernet Receives data bytes and stores in SDRAM(EMIF Synchronous mode)

New design:

1) Ethernet Receives data bytes and stores in SDRAM(EMIF Synchronous mode)

2) 100ms periodic application will request DMA to transfer data of 1000 bytes from SDRAM (EMIF Synchronous mode) to FPGA through EMIF Interface (Asynchronous mode).

Question:

As shown in the image, for transferring 1000 bytes we need 500 Asynchronous access cycles (EMIF 16 bit data).

Each Asynchronous cycle is of 40ns (Setup, Hold, Strobe, TA – 10ns each). So for 500 Asynchronous access cycles it takes 500 * 40ns = 2us.

As per Section 21.2.14.1 TMS570LC43x TRM

Asynchronous request < tRAS .

2us < 50ns --> Condition is not satisfied. Is this understanding correct?. Please share your view on this.

Thanks.