Other Parts Discussed in Thread: TI-CGT

Hi,

I'm trying to compile and flash some legacy code onto the corresponding legacy hardware based on the MSP430FG4618 for a further development project.

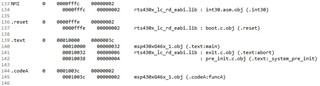

First I imported the legacy code into Code Composer Studio 10.3.1.00003 and compiled with TI-CGT 21.6.0 LTS. The build succeeded, but when I tried to flash the device, I got a data verification error:

MSP430: File Loader: Verification failed: Values at address 0x00010 do not match Please verify target memory and memory map.

According to the data sheets, 010h is the memory address of the P3REN register.

I haven't modified the linker script that CCS generated, and I verified that the address 010h was mapped correctly.

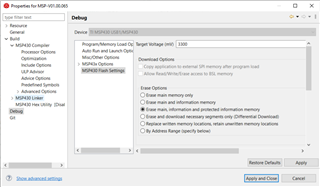

I also tried selecting the option to erase the main, information and protected information memory regions, but this didn't change anything.

When I try to flash another (small) program that I wrote from scratch to test the device (blink some LEDs, etc.), flashing and debugging work without problems.

Before I flashed the device, I had dumped the memory of the device with MSPFlasher into three files: main.txt (MAIN), info.txt (INFO), bootloader.txt (BSL):

C:\> MSP430Flasher -n MSP430FG4618 -r [main.txt,MAIN] C:\> MSP430Flasher -n MSP430FG4618 -r [info.txt,INFO] C:\> MSP430Flasher -n MSP430FG4618 -r [bootloader.txt,BSL]

When I tried to recover the old firmware with the following commands:

C:\> MSP430Flasher -n MSP430FG4618 -w main.txt -v -z [VCC=3300, RESET]

C:\> MSP430Flasher -n MSP430FG4618 -w info.txt -v -z [VCC=3300, RESET]

C:\> MSP430Flasher -n MSP430FG4618 -w bootloader.txt -v -z [VCC=3300, RESET]

main.txt succeeds, but info.txt and bootloader.txt fail with the same error:

* -----/|-------------------------------------------------------------------- *

* / |__ *

* /_ / MSP Flasher v1.3.20 *

* | / *

* -----|/-------------------------------------------------------------------- *

*

* Evaluating triggers...done

* Checking for available FET debuggers:

* Found USB FET @ COM14 <- Selected

* Initializing interface @ COM14...done

* Checking firmware compatibility:

* FET firmware is up to date.

* Reading FW version...done

* Setting VCC to 3300 mV...done

* Accessing device...done

* Reading device information...done

* Loading file into device...

# Exit: 59

# ERROR: Could not write device memory

* Starting target code execution...done

* Disconnecting from device...done

*

* ----------------------------------------------------------------------------

* Driver : closed (No error)

* ----------------------------------------------------------------------------

*/

What could be cause of these problems? How can I further investigate it?

Thank you in advance.