Other Parts Discussed in Thread: MSP430FR2433

I've discovered a design flaw in this board. When you are trying to debug an ISR which is bound to the RST/NMI pin while in NMI mode, the target's PC gets loaded with the wrong address and forces a crash. The PC should be getting loaded with the address to the ISR.

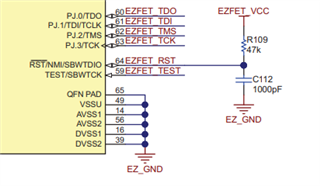

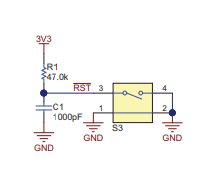

This is the cause. Switch S3 is connected to the RST/NMI pin on the emulator chip and the target chip. So when you close the switch, the emulator chip senses a reset signal while the target chip senses a NMI.

The target chip will only properly execute the ISR after the program is loaded and the debugger is closed.

Are you guys aware of this?