Hi Team,

We have received this report from our customer,

We have problems with a charge of your MSP430F5328 Microcontrollers.

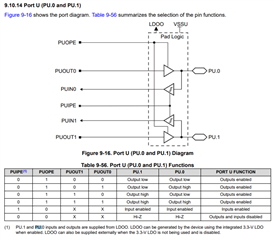

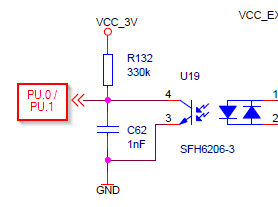

Some/Many Microcontrollers of this marking / charge seems to have a leakage current or something else, which leads to a fail behaviour. When the optokoppler is inactive the Voltage should be around 3.1V. In Fail PU.0 has 0V and PU.1 has 1.5V. Not all microcontrollers with the same marking are effected from this problem.

We've stopped the production, because of this issue. Please check and declare why there is a problem.

Some devices starts running if a measurement is taken with a multimeter. Some starts running on contact with PU.0 some with PU.1.

It seems the pull-up resistor is too high for this application. Can you please confirm?

Regards,

Danilo