Dear Sir

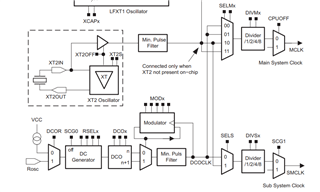

I feed an external 8MHZ clock signal to the XT2IN pin for the MSP430F2619S-HT with below configuration:

BCSCTL3 = XT2S_3; // select external clock singal: 8MHZ

BCSCTL1 &= ~XT2OFF; //XT2OFF = 0

BCSCTL2 = DIVM_0 + DIVS_0; //MCLK and SMCLK Divider is 1

I wish to see the clock output on the both the SMCLK and MCLK with scope, but I saw nothing.

How does this part works with an external clock signal

Clark Wang