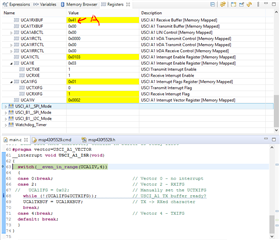

UART Tx ready interrupt (UCTXIFG) is been cleared by reading UCA1IV register, so how is the following ISR (This is taken from T.I. sample) suppose to work:

#pragma vector=USCI_A1_VECTOR

__interrupt void USCI_A1_ISR(void)

{

switch(__even_in_range(UCA1IV,4))

{

case 0:break; // Vector 0 - no interrupt

case 2: // Vector 2 - RXIFG

// UCA1IFG = 0x02; // Manually set the UCTXIFG

while (!(UCA1IFG&UCTXIFG)); // USCI_A1 TX buffer ready?

UCA1TXBUF = UCA1RXBUF; // TX -> RXed character

break;

case 4:break; // Vector 4 - TXIFG

default: break;

}

}

Below, Rx Buffer has received the "A" from UART and it should put into the Tx buffer next if it's empty (i.e. ready to send), but UCTXIFG was never set. So it waits there forever. If I manually set the UCTXIFG, then it would work, then what's the point of the while loop to wait for the UCTXIFG to be set if I am manually set it right before?