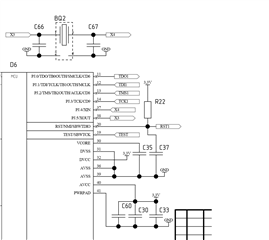

I try to configure a clock scheme as: "crystal oscillator 20MHz -> XTAL1 -> SMCLK". Divider I set to 4.

The program with the code that I configure a clock and the crystal connection scheme is below. I expect take a 5 MHz at the SMCLK out pin (PJ.0), but the 1.22 MHz I having in result. I don't understand why and very do hope for advice why it may be.

#include <msp430.h>

#ifndef __DATATYPES_H__

#define __DATATYPES_H__

typedef char int8_t;

typedef unsigned char uint8_t;

typedef int int16_t;

typedef unsigned int uint16_t;

typedef long int32_t;

typedef unsigned long uint32_t;

typedef uint8_t BYTE;

#endif

/**

* main.c

*/

inline void __ClkConf(void);

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // stop watchdog timer

__ClkConf();

while(1)

{

}

return 0;

}

inline void __ClkConf(void)

{

uint16_t temp;

PJSEL0 |= BIT0;

PJSEL1 &= ~((uint16_t)BIT0);

PJDIR |= BIT0 + BIT4 + BIT5;

PJOUT |= BIT0 + BIT4 + BIT5;

PJSEL0 |= BIT4 + BIT5; // connect pins to xtal;

CSCTL0_H = 0xA5;

CSCTL1 |= DCOFSEL0 + DCOFSEL1; // Set max. DCO setting

CSCTL2 = SELA_3 + SELS_0 + SELM_3; // set ACLK = MCLK = DCO; SMCLK = XTAL1

CSCTL3 = DIVA_0 + DIVS_2 + DIVM_0; // set all dividers

temp = CSCTL4;

temp |= XTS;

temp &= ~(XT1OFF);

CSCTL4 = temp;

}