Hello all...

Using an EZ430-2013 dev board with the following small app code .....

I am finding that if I port out the ACLK (the code below has this line removed P1SEL |= BIT0; as I was just using the LED on the dev board) and remove LPM3_bits below the divisor works just fine but when I put LPM3_bits back into the code the ACLK (which is assigned the VLO clk) never changes its' frequency....Can someone tell me why?

int main(void)

{

BCSCTL1 |= DIVA_3; // ACLK/2

BCSCTL3 |= LFXT1S_2; // ACLK = VLO

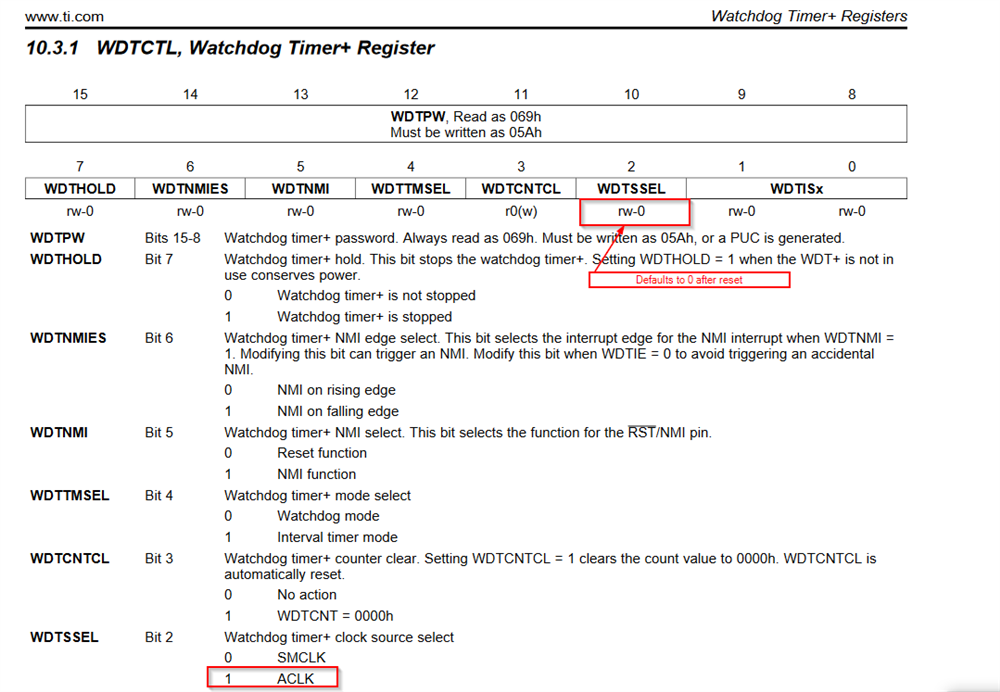

WDTCTL = WDT_ADLY_1000; // Interval timer

IE1 |= WDTIE; // Enable WDT interrupt

P1DIR |= 0x01; // Set P1.0 to output direction

__bis_SR_register(LPM3_bits + GIE); // Enter LPM3 w/interrupt

}

#pragma vector=WDT_VECTOR

__interrupt void watchdog_timer(void)

{

P1OUT ^= 0x01; // Toggle P1.0 using exclusive-OR

}