Dear Team,

A strange problem suddenly arised which we have no clue about, could you please help here ?

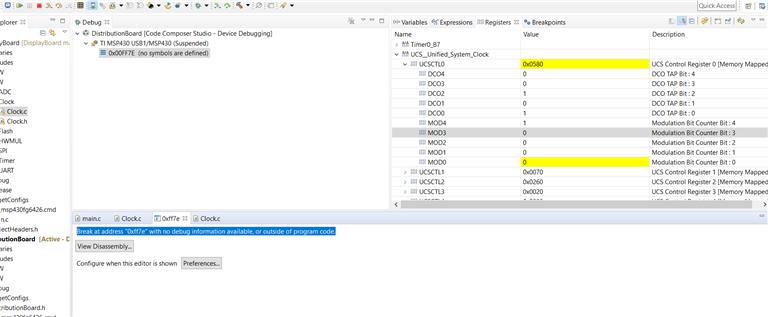

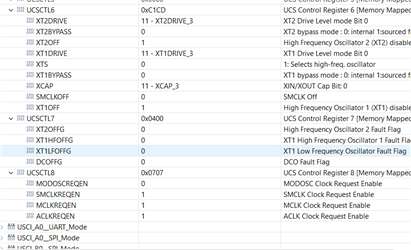

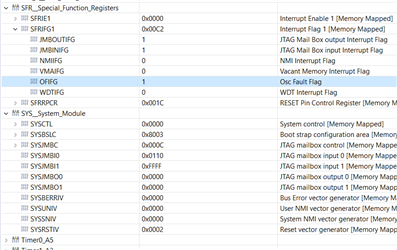

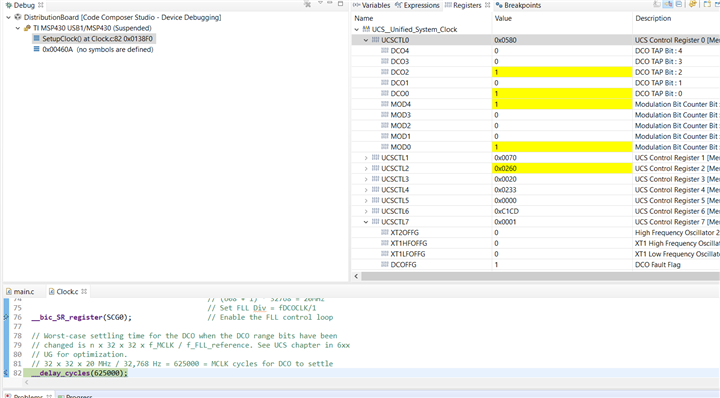

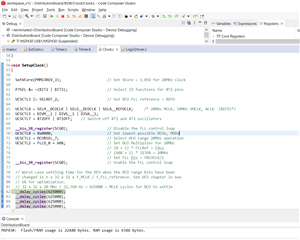

When we flash our software in debug session the code runs well until the first hit of __delay_cycles and does not proceed further from here. Whenever i pause the execution the break point stays here and does not proceed..

But the same code runs well and my software functions normal with the same software without the debug session (just stopped the debug sessions and hit the reset button on the board). the same software in release mode is running in some of our units without any issues.

I tried to recreate a fresh project and import the sources and the debug session works for the very first instance, and the problem comes up again from the second debug session onwards. Not sure where things are going wrong and need your support here.

I have placed my code here for reference

https://drive.google.com/file/d/1FmchPJjhVtBZjGTt-U79aiARngcFVcnF/view?usp=sharing

Thanks

Surya