Other Parts Discussed in Thread: MSP-TS430PZ100AUSB

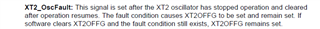

I've tried setting the clock, but I keep getting UCSCTL7.XT2OFFG=1 (Falt error on XT2).

WDTCTL = WDTPW | WDTHOLD; // Disable the Watchdog

CTSD16CCTL0 |= CTSD16SC; // Workaround for CTSD16OFFG errata

do

{

CTSD16CTL &= ~CTSD16OFFG;

}while (CTSD16CTL&CTSD16OFFG); // End of CTSD16OFFG workaround

while(BAKCTL & LOCKBAK){ // Unlock XT1 pins for operation

BAKCTL &= ~(LOCKBAK);

}

UCSCTL6 &= ~(XT1OFF); // XT1 On

UCSCTL6 |= XCAP_2; // Internal load cap

UCSCTL6 |= XT2OFF; // XT2 OFF

// Loop until XT1 fault flag is cleared

do

{

UCSCTL7 &= ~(XT2OFFG | XT1LFOFFG | DCOFFG); // Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while ((UCSCTL7 && (XT2OFFG | XT1LFOFFG | DCOFFG))==0); // oscillator fault flag

UCSCTL6 &= ~(XT1DRIVE_3); // Xtal is now stable, reduce drive strength

// [System Clock/FLL+]

UCSCTL0 = 0x0000;

UCSCTL1 = 0x0020;

UCSCTL2 = 0x0079;

UCSCTL3 = 0x0000;

UCSCTL4 = 0x0033;

UCSCTL5 = 0x0000;

UCSCTL6 = 0x0084;

UCSCTL8 = 0x0007;

UCSCTL7 &= ~(XT2OFFG | XT1LFOFFG | DCOFFG);

do{

UCSCTL7 &= ~(XT2OFFG | XT1LFOFFG | DCOFFG); // Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while ((UCSCTL7 && (~(XT2OFFG | XT1LFOFFG | DCOFFG)))==0);// oscillator fault flag

I'm using MSP-TS430PZ100AUSB (evaluation board), but I don't use XT2, so I set UCSCTL6.XT2OFF=0, but a Fault error occurs.

I'm having trouble figuring out the cause.

Could you give me some advice?