I'm having trouble with the long CTSD16 conversion time.

Please tell me the reason.

The main settings of CTSD are as follows.

Sampling rate = 32 clocks

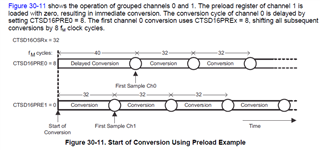

PreloadValue=0 clock

CTSD16INTDLY=1b (First sample causes interrupt)

CTSD16RRI=1b (Rail-to-rail input enabled)

Continuous conversion mode

SMCLK=4MHz

The conversion result is stored in the buffer memory by DMA.

After conversion for the specified number of times, CTSD conversion is stopped by a DMA interrupt.

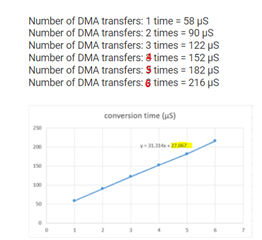

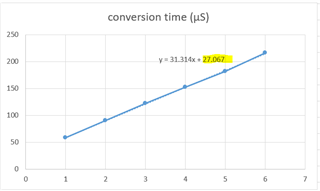

The time from the start of CTSD conversion to the stop of CTSD conversion by a DMA interrupt is shown below.

Number of DMA transfers: 1 time = 58 μS

Number of DMA transfers: 2 times = 90 μS

Number of DMA transfers: 3 times = 122 μS

Number of DMA transfers: 3 times = 152 μS

Number of DMA transfers: 3 times = 182 μS

Number of DMA transfers: 3 times = 216 μS

The vertical axis is the conversion time, and the horizontal axis is the number of DMA transfers.

Approximately 27µS is added to all conversion times.

What do you think is the reason for adding this 27μS?