Other Parts Discussed in Thread: TIDM-THREEPHASEMETER-F6779

I am developing code for a level 2 electric vehicle car charger. I am using the example code from the Three Phase power meter(TIDM-THREEPHASEMETER-F6779).

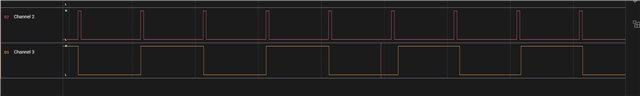

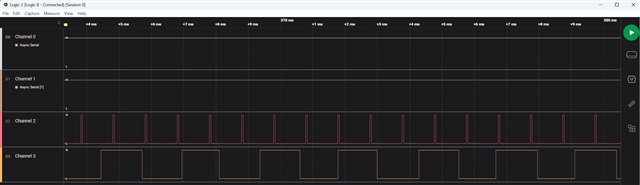

I am generating a PWM signal using Timer 2 as shown in the code below. I am trying to measure the voltage of the PWM signal at a 5% duty cycle. The picture below shows the PWM signal on top and then the bottom is a pin I am toggling to show when the ADC will sample the PWM signal.

Why doesn't the TIMER2_A0 interrupt fire every time the Timer reaches TA2CCR0? Shouldn't TIMER2_A0 interrupt fire right when the PWM signal goes from low to high?

Is there a better way to measure the voltage of the PWM signal?

/* Set Initial PWM Period 1kHz */

TA2CCR0 = 16685 - 1; //32786 Hz clock divided by 2 with some offset. The -1 comes from timer counting from 0 and not 1.

/* CCR0 reset/set */

TA2CCTL1 = OUTMOD_7;

TA2CCTL0 = CCIE; // CCR0 interrupt enabled

CURRENT_RATING = 5.0;

CURRENT_RATING = CURRENT_RATING / 100.0;

TA2CCR1 = 16685.0 * CURRENT_RATING;

/* SMCLK, up mode, clear TAR */

TA2CTL = TASSEL_2 | MC_1 | TACLR | TAIE;

/******* Enable Pilot Wire PWM ******/

P11DIR |= BIT3;

P11SEL0 |= BIT3;

P11OUT &= ~BIT3;

#pragma vector=TIMER2_A0_VECTOR

__interrupt void Timer2_ISR (void)

{

P9OUT ^= BIT0; //Toggle pin

ADC10CTL0 |= ADC10ENC + ADC10SC;

}

Thanks for the help,

Mike