Hello Friends

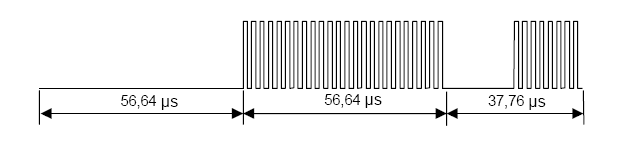

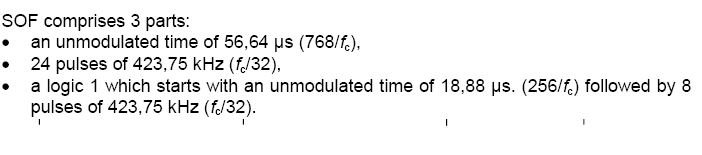

Am working on a project where i have to generate chain of pulses as printed below. I have to generate SOF and EOF

For starting a frame, i want to generate clock pulses as below with the following duration

Am using below document as reference.

I couldnt able to generate the above pulses with the present MSP430F2350 am using.

Help appreciated

Regards

Nanda