Hi;

We are using MSP430F2350 with a 32768Hz tuning fork crystal from Citizen:CFS-206 on our metering modules. No external load capacitors are connected,but internally XCAPX =3.We mounted the modules and after a while( 1months later),we could not communicate with some of them via M-bus.We are using TSS721A M-bus IC on slave (our modules)

We suspected from XOSC8 erratum.Thus we made some measurements over crystal.ACLK duty cycle is measured to be > %30 and < %50

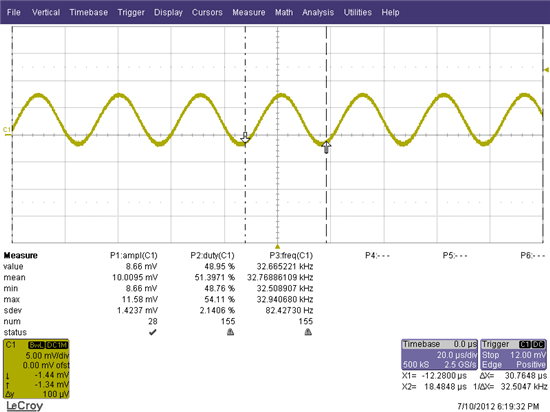

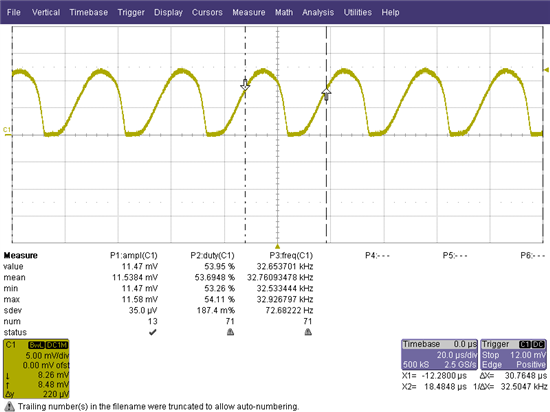

There exists a distorted and saturated sine wave signal at Xout pin.Xin signals looks as a sine wave. Please find the images below(please note that scale is 5mV and measurement is done via X100 probe ,each square equals 500mV)

Xin:

Xout:

I have a few questions about crystal:

Are these signals seem okay for a stable oscillation?Does the pierce oscillator inside the mcu damp the signal such that after a while ACLK falls below %30 duty?

Is there an overdrive issue exist due to saturating the crystal?

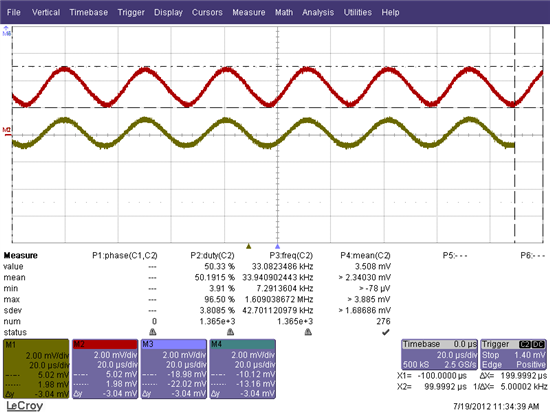

We use same crystal with another TI mcu:MSP430F4793 and the Xin(yellow) and Xout(red) signals given below(please note that scale is 2mV and measurement is done via X100 probe ,each square equals 200mV)

Thank you