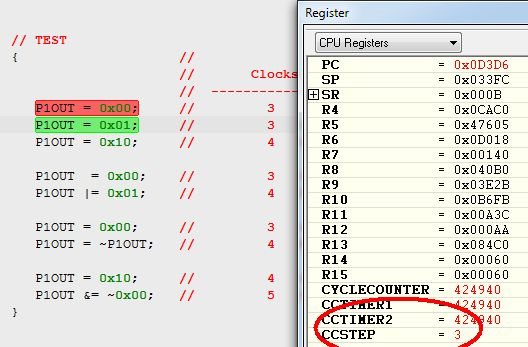

Here you can see the Test-Code, the measured cycles and the Assembler-Code for the different µController

// TEST

// MSP430F5310 MSP430G2353

// Clocks Code Clocks Code

// -----------------------------------------------------------------------------------------------------------------------

P1OUT = 0x00; // 3 43C2 0202 clr.b &PAOUT 4 43C2 0202 clr.b &PAOUT

P1OUT = 0x01; // 3 43D2 0202 mov.b #0x1,&PAOUT 4 43D2 0202 mov.b #0x1,&PAOUT

P1OUT = 0x10; // 4 40F2 0010 0202 mov.b #0x10,&PAOUT 5 40F2 0010 0202 mov.b #0x10,&PAOUT

P1OUT = 0x00; // 3 43C2 0202 clr.b &PAOUT 4 43C2 0202 clr.b &PAOUT

P1OUT |= 0x01; // 4 D3D2 0202 bis.b #0x1,&PAOUT 4 D3D2 0202 bis.b #0x1,&PAOUT

P1OUT = 0x00; // 3 43C2 0202 clr.b &PAOUT 4 43C2 0202 clr.b &PAOUT

P1OUT = ~P1OUT;// 4 E3F2 0202 inv.b &PAOUT 4 E3F2 0202 inv.b &PAOUT

P1OUT = 0x10; // 4 40F2 0010 0202 mov.b #0x10,&PAOUT 5 40F2 0010 0202 mov.b #0x10,&PAOUT

P1OUT &= ~0x00;// 5 42D2 0202 0202 mov.b &PAOUT,&PAOUT 6 42D2 0202 0202 mov.b &PAOUT,&PAOUT

Why does the MSP430G2353 often needs one more cycle ???

I used IAR-Workbench V5.50.2, and tested it in the simulator and on chip.

Do you have an idea ?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.