I'm experiencing some problems in my project based on a CC430F6147 & CC430F5147 microcontroller.

The microcontroller's digital voltage (DVcc) runs on 3V, and the VCore is being set from value 0 to value 2 (stepwise via the SetVCore hal_pmm library function) to be able to have proper RF transmission.

In the final product, the DVcc needs to run at 2.5V, and there the problem arises:

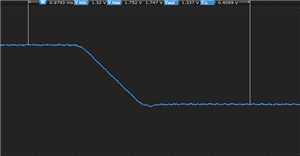

When no JTAG is connected, everything works as expected, but when the JTAG connection is used, the SW does get in an undefined state right after setting the VCore to value 2 (1.8V):

unsigned int SetVCoreUp (unsigned char level)

{

...

PMMCTL0_L = PMMCOREV0 * level;

// Wait until new level reached

if (PMMIFG & SVMLIFG)

while ((PMMIFG & SVMLVLRIFG) == 0);

...

--> I'm still breaking on the "if" statement when stepping through the code, but a step to the next line gets me timeout of the jtag connection (I can still see activity on the JTAG lines, and no reset of the device).

Another effect I can see, is that when starting a debug session, it sometimes can not erase the flash, although I can see a lot of traffic on the TDI & TDO pins:

>MSP430: Trouble Writing Memory Block at 0x8000 on Page 0 of Length 0x4986: Could not erase device memory

A second attempt is always successfull to download & start the application. (I tend to believe that i always see this behaviour when the device has been powered off first)

I'm using an MSP-FET430UIF usb debugger interface and the JTAG debugger is not powering the board.

The DVCC is connected through pin 2 back to the debugger for voltage reference. In CSS, i've changed the output voltage from 3 to 2.5V.

Additionally I've tried following things with no luck:

- first run the code on 3V, then lower in the middle of the execution the voltage to 2.5V. I see that debugging is not working anymore (break instruction doesn't break: >MSP430: Trouble Halting Target CPU: Internal error)

- I've both tried on CCS5.5 with compiler version 4.2 and a version of IAR where i don't recall the version number from.

- moved back to an development board: EM430F6147RF900

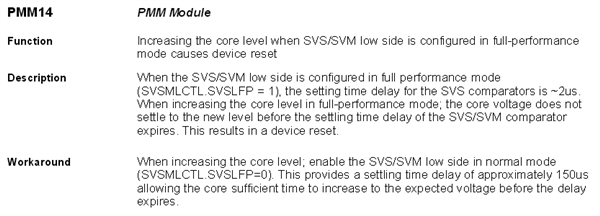

- Disabled SVS & SVM when changing the core voltage. The rise times do differ a bit between 2.5 & 3V DVCC. A rise time of arround 100µs is being noticed)

It would be appreciated if anyone could give me a hint on what i'm doing wrong here.

Code snippet of what is being run (DEBUG is set):

#ifdef DEBUG

/**

* This is run before main with GCC compiler.

*/

int _system_pre_init()

{

/* Stop the WD here for CSS to be able to debug.*/

watchdog_Disable();

return 1;

}

#endif

void main(void)

{

#ifdef DEBUG //repeat for IAR

watchdog_Disable();

#endif

debug_initcheckStackCorruption();

/* Increase PMMCOREV level to 2 for proper radio operation */

SetVCore(2);

...