Hello,

I am facing a problem that driving me crazy.

I am trying to increase MCLK/SMCLK of the MSP430F5436A (MSP-EXP430F5438A) with the following code:

void initClk(void)

{

SetVcoreUp (PMMCOREV_1); //Increase slowly Vcore

SetVcoreUp (PMMCOREV_2); //Increase slowly Vcore

SetVcoreUp (PMMCOREV_3); //Increase slowly Vcore to work with DCO = 25MHz

P11DIR |= BIT0 | BIT1 | BIT2; // Set pin 11.0,11.1,11.2 to output ACLK, MCLK, SMCLK

P11SEL |= BIT0 | BIT1 | BIT2; // Select pin 11.0,11.1,11.2 to output ACLK, MCLK, SMCLK

UCSCTL3 = SELREF__REFOCLK; // select REFO as FLL source

UCSCTL6 = XT1OFF | XT2OFF; // turn off XT1 and XT2

/* Initialize DCO to 25.00MHz */

__bis_SR_register(SCG0); // Disable the FLL control loop

UCSCTL0 = 0x1f<<8; // Set possible DCOx=31, MODx=0

UCSCTL1 = DCORSEL_4; // Set DCORSELx for DCO = 12.3 MHz - 28.2 MHz

UCSCTL2 = 625u; // Set DCO Multiplier for 20.5MHz

// (N + 1) * FLLRef = Fdco

// (625 + 1) * 32768 = 20.5MHz

UCSCTL4 = SELA__REFOCLK | SELS__DCOCLK | SELM__DCOCLK;

// Select Aclock = REF0CLK

// Select SMclock = DCOCLK

// Select Mclock = DCOCLK

__bic_SR_register(SCG0); // Enable the FLL control loop

// Worst-case settling time for the DCO when the DCO range bits have been

// changed is n x 32 x 32 x f_MCLK / f_FLL_reference. See UCS chapter in 5xx

// UG for optimization.

// 32*32*20.5MHz/32768Hz = 640625 = MCLK cycles for DCO to settle

__delay_cycles(640625);

/* Loop until XT1,XT2 & DCO fault flag is cleared */

do

{

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + XT1HFOFFG + DCOFFG);

// Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}

while (SFRIFG1&OFIFG); // Test oscillator fault flag

}

while the SetVcoreUp is:

void SetVcoreUp (unsigned int level)

{

// Open PMM registers for write

PMMCTL0_H = PMMPW_H;

// Set SVS/SVM high side new level

SVSMHCTL = SVSHE + SVSHRVL0 * level + SVMHE + SVSMHRRL0 * level;

// Set SVM low side to new level

SVSMLCTL = SVSLE + SVMLE + SVSMLRRL0 * level;

// Wait till SVM is settled

while ((PMMIFG & SVSMLDLYIFG) == 0);

// Clear already set flags

PMMIFG &= ~(SVMLVLRIFG + SVMLIFG);

// Set VCore to new level

PMMCTL0_L = PMMCOREV0 * level;

// Wait till new level reached

if ((PMMIFG & SVMLIFG))

while ((PMMIFG & SVMLVLRIFG) == 0);

// Set SVS/SVM low side to new level

SVSMLCTL = SVSLE + SVSLRVL0 * level + SVMLE + SVSMLRRL0 * level;

// Lock PMM registers for write access

PMMCTL0_H = 0x00;

}

From the Data Sheet of the msp430f5436a:

for DCORSELx = 4, DCOx = 31, MODx = 0 - the MCLK is between 12.3MHz and 28.2 MHz.

I use the following formula to create 20.5MHz CLK:

(N + 1) * FLLRef = Fdco

(625 + 1) * 32768 = 20.5MHz

=> N=625.

the problem is that it sometimes work, and sometimes not.

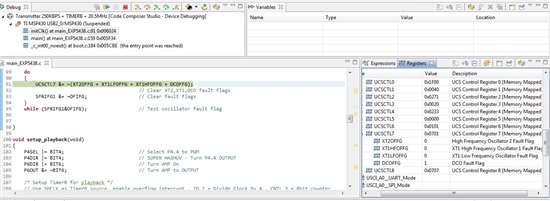

when it's not working, its either stuck on the "__delay_cycles(640625);" line, or it has a DCO Fault Flag:

I have tried it with a different CPU ( the MSP430F5438A) and still it doesn't work all the time.

Please help, i just want a 20.5MHz MCLK.

P.S

I do not have any other EXT crystal.