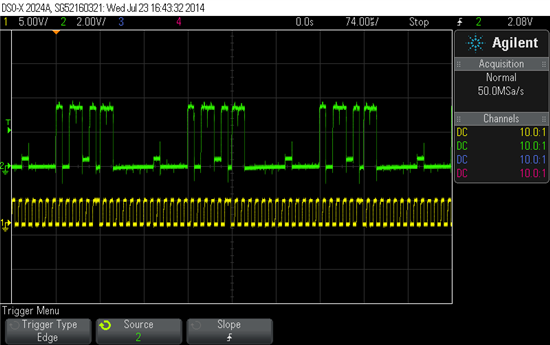

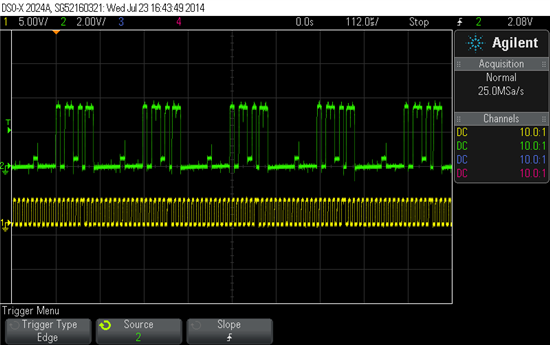

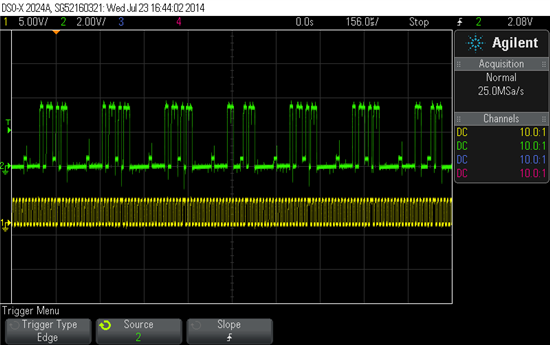

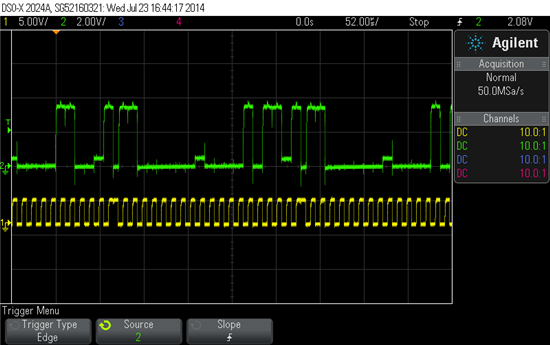

I have tried the sample code for the MSP430F5529 with teh change to have it working on B1 as opposed to B0. I have posted the code below in its charged form. The issue I am getting is there does not appear to be any intelligent output from the I2C module, I have included a logic capture below.

#include <msp430.h>

unsigned char *PTxData; // Pointer to TX data

unsigned char TXByteCtr;

const unsigned char TxData[] = // Table of data to transmit

{

0x11,

0x22,

0x33,

0x44,

0x55

};

int main(void)

{

unsigned int i;

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

P4SEL |= 0x06; // Assign I2C pins to USCI_B0

UCB1CTL1 |= UCSWRST; // Enable SW reset

UCB1CTL0 = UCMST + UCMODE_3 + UCSYNC; // I2C Master, synchronous mode

UCB1CTL1 = UCSSEL_2 + UCSWRST; // Use SMCLK, keep SW reset

UCB1BR0 = 12; // fSCL = SMCLK/12 = ~100kHz

UCB1BR1 = 0;

UCB1I2CSA = 0x48; // Slave Address is 048h

UCB1CTL1 &= ~UCSWRST; // Clear SW reset, resume operation

UCB1IE |= UCTXIE; // Enable TX interrupt

while (1)

{

for(i=0;i<10;i++); // Delay required between transaction

PTxData = (unsigned char *)TxData; // TX array start address

// Place breakpoint here to see each

// transmit operation.

TXByteCtr = sizeof TxData; // Load TX byte counter

UCB1CTL1 |= UCTR + UCTXSTT; // I2C TX, start condition

__bis_SR_register(LPM0_bits + GIE); // Enter LPM0, enable interrupts

__no_operation(); // Remain in LPM0 until all data

// is TX'd

while (UCB1CTL1 & UCTXSTP); // Ensure stop condition got sent

}

}

//------------------------------------------------------------------------------

// The USCIAB0TX_ISR is structured such that it can be used to transmit any

// number of bytes by pre-loading TXByteCtr with the byte count. Also, TXData

// points to the next byte to transmit.

//------------------------------------------------------------------------------

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector = USCI_B1_VECTOR

__interrupt void USCI_B1_ISR(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(USCI_B1_VECTOR))) USCI_B1_ISR (void)

#else

#error Compiler not supported!

#endif

{

switch(__even_in_range(UCB1IV,12))

{

case 0: break; // Vector 0: No interrupts

case 2: break; // Vector 2: ALIFG

case 4: break; // Vector 4: NACKIFG

case 6: break; // Vector 6: STTIFG

case 8: break; // Vector 8: STPIFG

case 10: break; // Vector 10: RXIFG

case 12: // Vector 12: TXIFG

if (TXByteCtr) // Check TX byte counter

{

UCB1TXBUF = 0x0C;//*PTxData++; // Load TX buffer

TXByteCtr--; // Decrement TX byte counter

}

else

{

UCB1CTL1 |= UCTXSTP; // I2C stop condition

UCB1IFG &= ~UCTXIFG; // Clear USCI_B0 TX int flag

__bic_SR_register_on_exit(LPM0_bits); // Exit LPM0

}

default: break;

}

}

I have also tried my own code which is below also which I can not get working. Any help would be much appreciated.

#include <msp430f5529.h>

int initI2C(){

P4SEL |= 0X60;

UCB1CTL1 = UCSWRST;

UCB1CTL0 = UCMST + UCMODE_3 +UCSYNC;

UCB1CTL1 = UCSSEL_2 + UCSWRST;

UCB1BR0 = 12; //fSCL = SMCLK/12 = ~100kHz

UCB1BR1 = 0;

}

int sendI2C(){

UCB1I2CSA = 0x60; //Set Slave Address

UCB1CTL1 &= ~UCSWRST; // Clear SW reset, resume operation

// UCB1IE |= UCTXIE; // Enable TX interrupt

UCB1CTL1 |= UCTR + UCTXSTT; // I2C TX, start condition

UCB1TXBUF = 0x0C

}

int main(){

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

initI2C();

sendI2C();

}

//------------------------------------------------------------------------------

// The USCIAB0TX_ISR is structured such that it can be used to transmit any

// number of bytes by pre-loading TXByteCtr with the byte count. Also, TXData

// points to the next byte to transmit.

//------------------------------------------------------------------------------

__interrupt void USCI_B1_ISR(void){

switch(__even_in_range(UCB1IV,12))

{

case 0: break; // Vector 0: No interrupts

case 2: break; // Vector 2: ALIFG

case 4: break; // Vector 4: NACKIFG

case 6: break; // Vector 6: STTIFG

case 8: break; // Vector 8: STPIFG

case 10: break; // Vector 10: RXIFG

case 12: // Vector 12: TXIFG

UCB1TXBUF = 0xC0; // Load TX buffer

UCB1CTL1 |= UCTXSTP; // I2C stop condition

UCB1IFG &= ~UCTXIFG; // Clear USCI_B0 TX int flag

__bic_SR_register_on_exit(LPM0_bits); // Exit LPM0

default: break;

}

}

Thanks