Hello TI E2E forum:

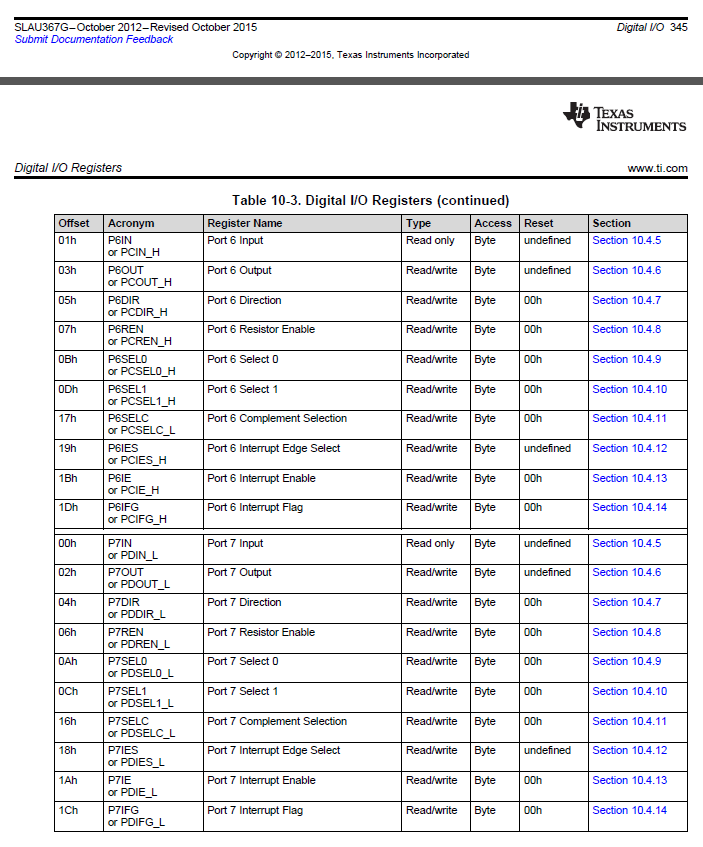

I am looking for some documentation / CCS clarification. I'm trying to initialize an MSP430FR6989 for my design. The User guide shows that there are interrupts on all GPIO ports and shows the address for the interrupt flags for each port (e.g. P1IFG), but the Code Composer “Include” file (msp430fr6979.h) does not define P5IFG, nor P6IFG-P10IFG.

Are they missing from the chip or from the documentation?

I am planning to use the 100-pin version so it should have all the options in this family.

Any feedback or input on this is welcomed and appreciated!

Thanks again!

Paul