Other Parts Discussed in Thread: MSP430FR6989

Hello

I am using the LaunchPad Eval Kit with the MSP430FR69891 uP.

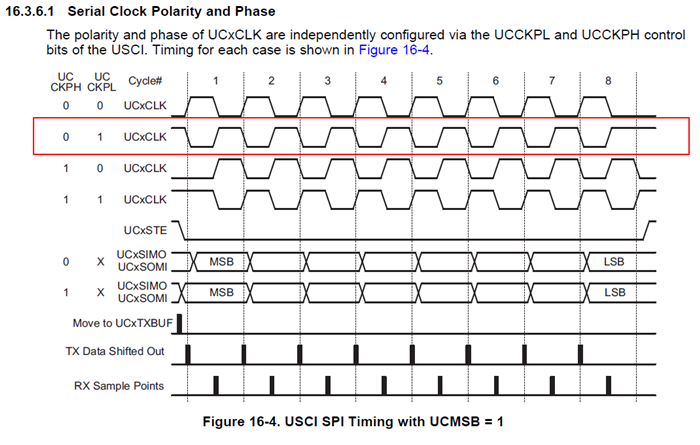

I want to use the SPI Interface USCIA0 in slave mode, 4 pin mode active high, with clock phase flag UCCKPH=1 enabled

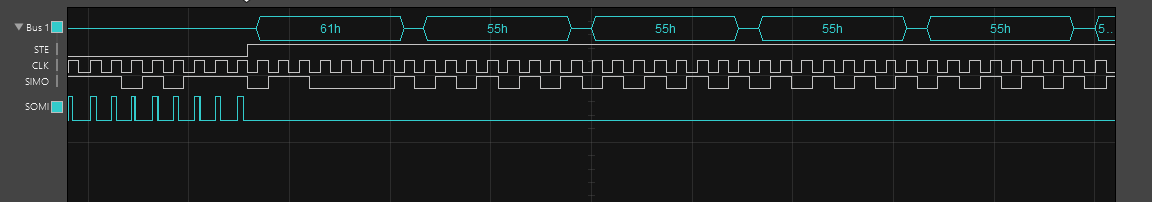

I have the UCA0IE set and also GIE is set. On the Logic Analyzer i can see that the UCA0STE pin goes high, the clock is working the data (SIMO) is correct but the interrupt gets not activated.

I could observe that if i don't set the UCCKPH (UCCKPH=0) the interrupts are working and also if i do the configuration of the SPI interface with the UCSWRST=0 (which is incorrect) it is also working,

I am using CCS 7 with GNU compiler (GNU v6.2.1.16 DOMNIUM Technologies Limited)

Here my configuration:

void initializeUca0Spi(void)

{

// Configure USCI_A0 for SPI operation

UCA0CTLW0 = UCSWRST; // **Put state machine in reset**

#if (RX_MODE == 1)

UCA0CTLW0 |= UCSYNC | UCMSB | UCCKPH | UCMODE_1;

#else

UCA0CTLW0 |= UCSYNC | UCMSB | UCCKPH;

#endif

UCA0CTLW0 &= ~UCSWRST;

#if (RX_MODE == 1)

UCA0IE |= UCRXIE;

__no_operation();

#endif

}

any ideas?

Thanks in advance